第四课 整数运算

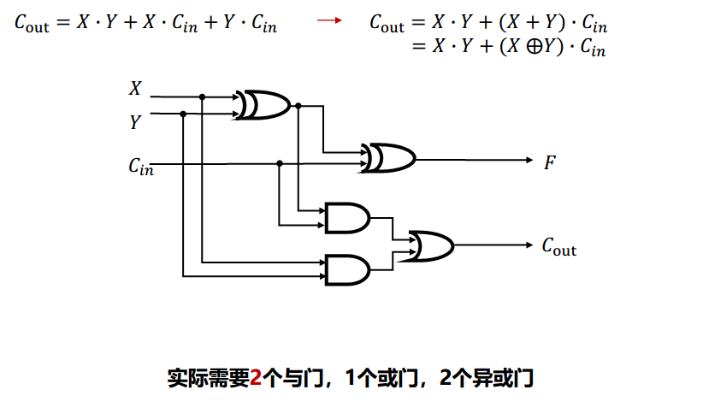

加法器

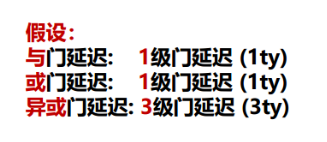

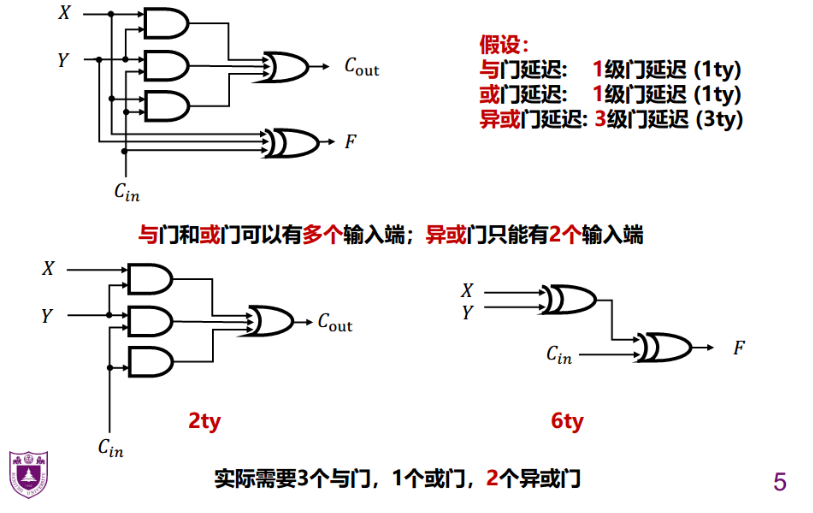

全加器

第一种

第二种

公式

其中,并非 的返回值为真,而是因为和前面的X与Y相配合,刚好形成了对应的结果

那么这种改善的好处是,减少了与门的使用

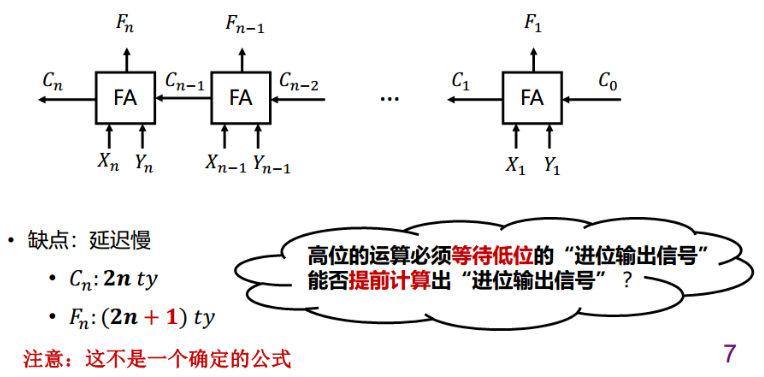

串行进位(行波进位)加法器

- 1位加法:

- 第i位加法:

Cn 是2n的延迟,原因是每个延迟为2:与操作+或操作

Fn是2n+1的延迟,原因是,

其中,

额外+3 是因为F产生的延迟。需要注意的是

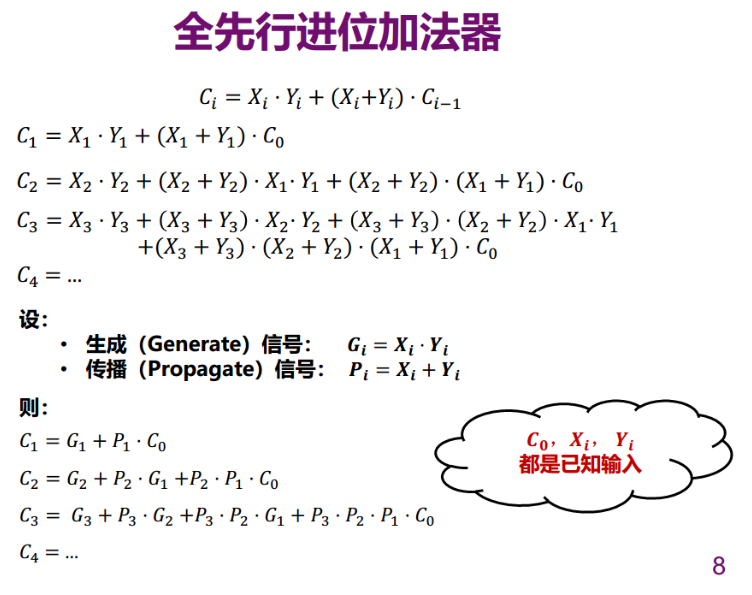

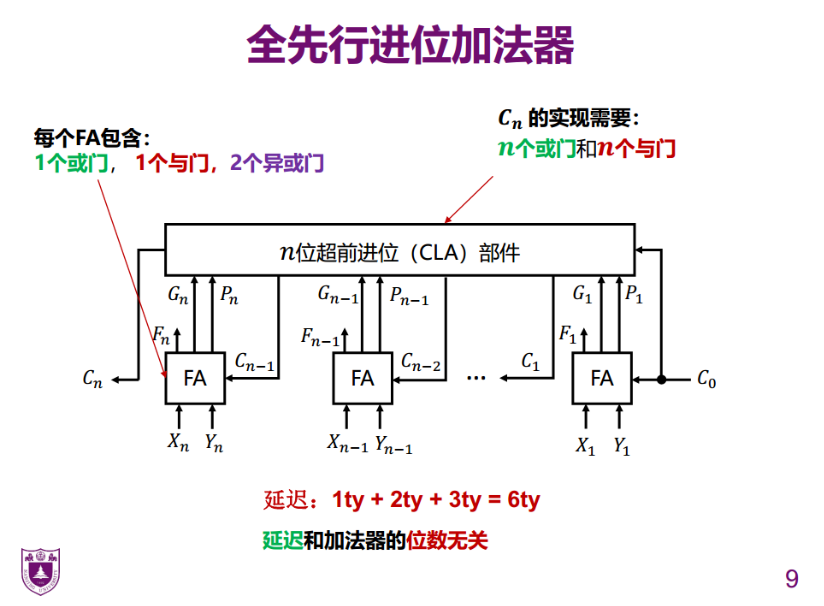

全先行进位加法器

- 1ty:代表的是生成信号和传播信号的生成

- 2ty:代表的是第i个进位信号的生成:1延迟的与运算+1延迟的或运算【与运算和或运算可以接受任意个数的参数】

- 3ty:代表的是第i个本位的生成:3延迟的或运算【和之前的1+2并行消耗,先计算X和Y的异或运算,经过3延迟后,C也得到了】+3延迟的或运算

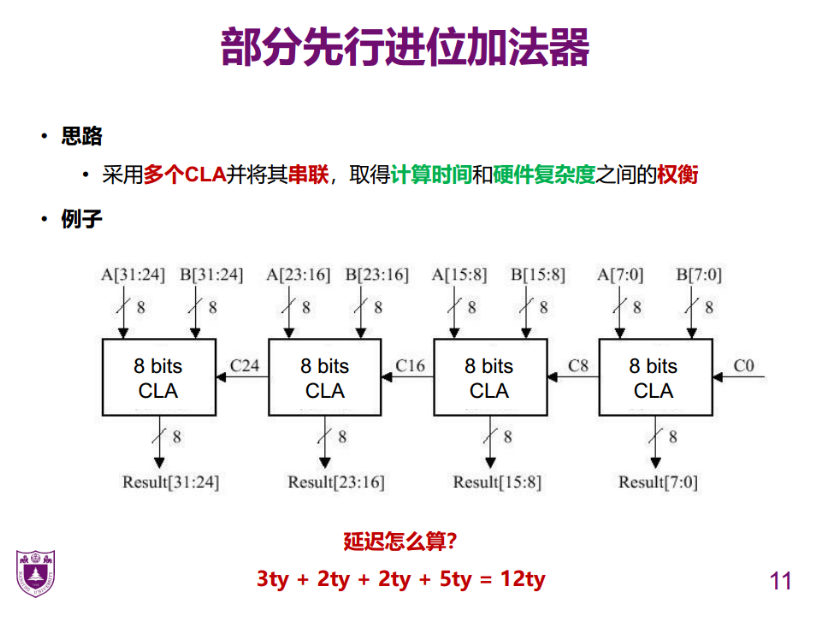

部分先行进位加法器

- 3ty=2ty+1ty

在最开始时,

此时的计算需要最初的1ty,之后,再根据计算公式可知需要2ty的延迟来生成

因此总延迟为3

四则运算

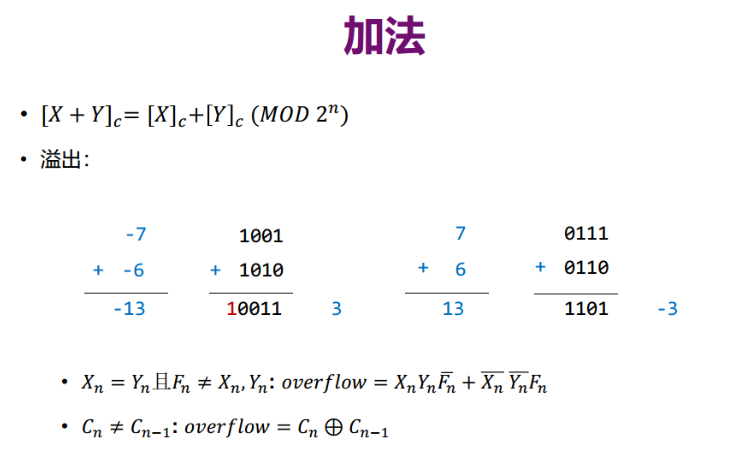

加法

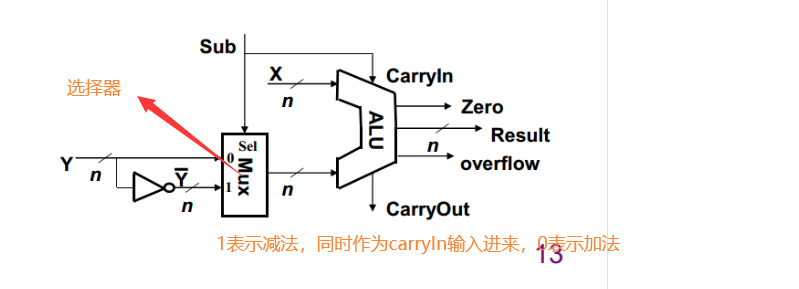

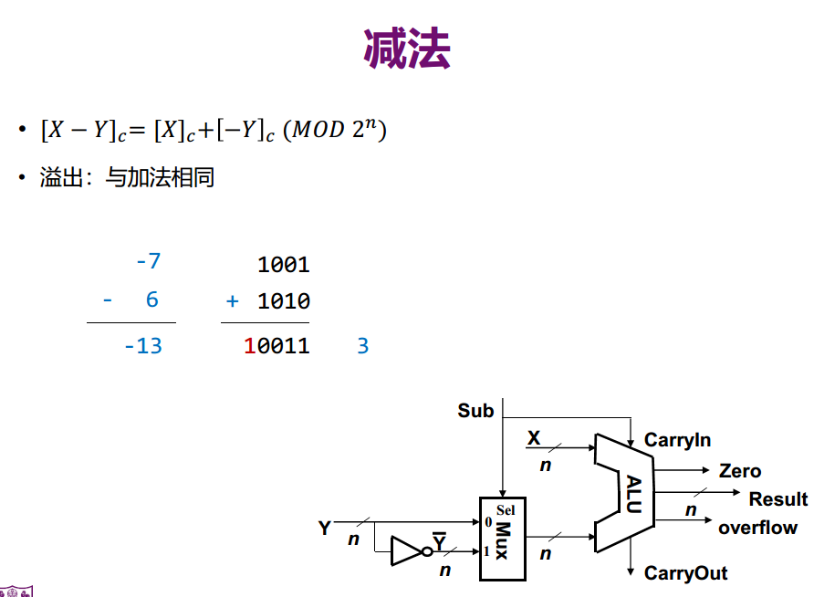

减法

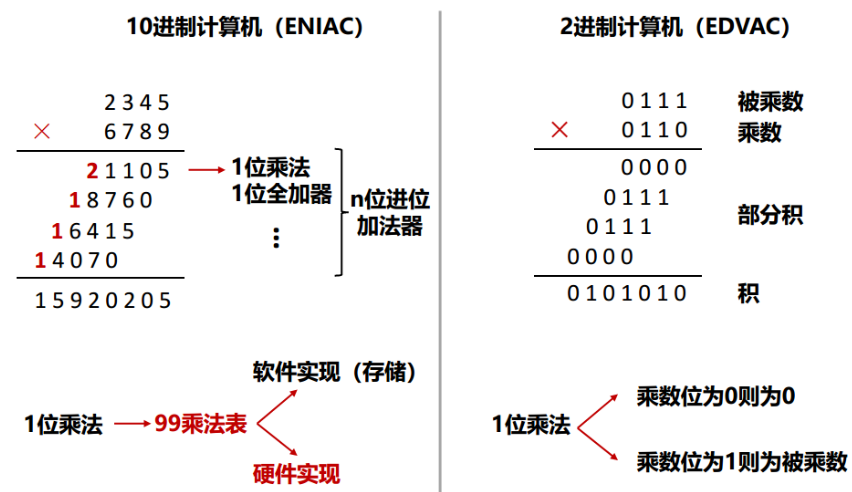

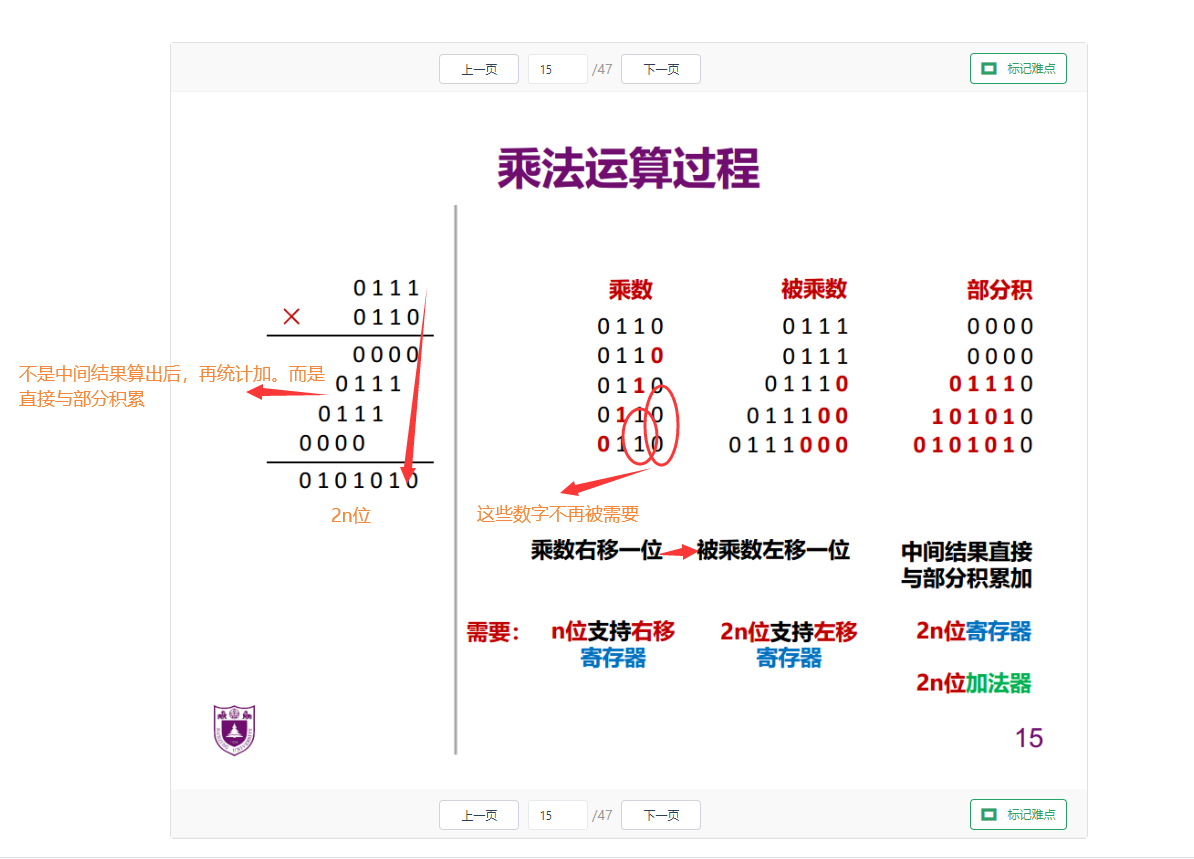

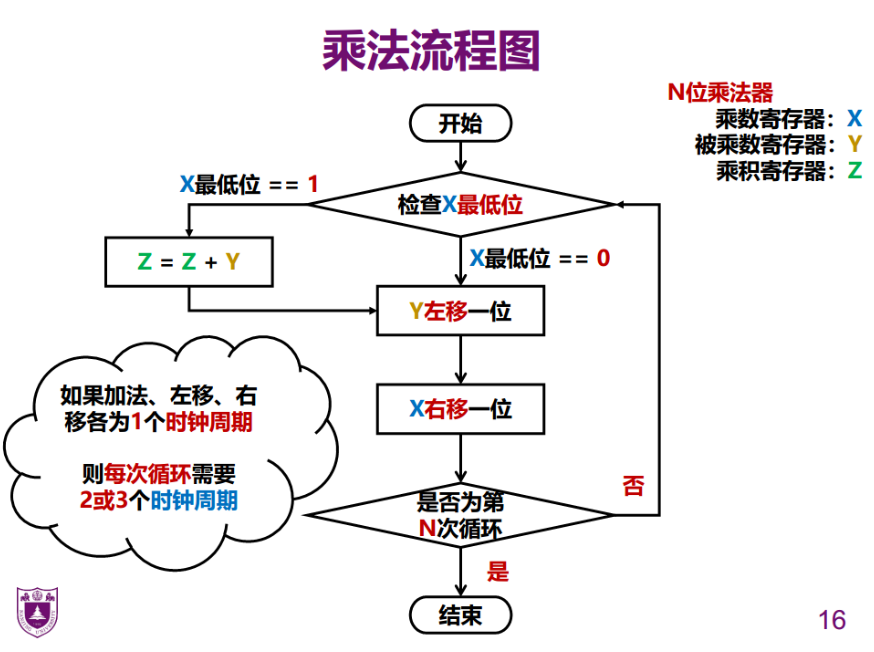

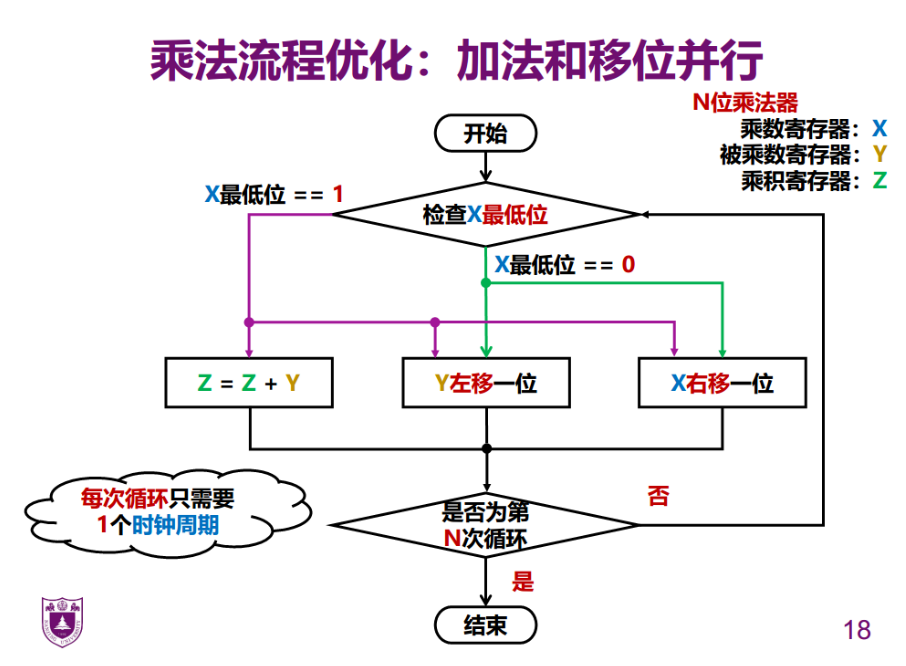

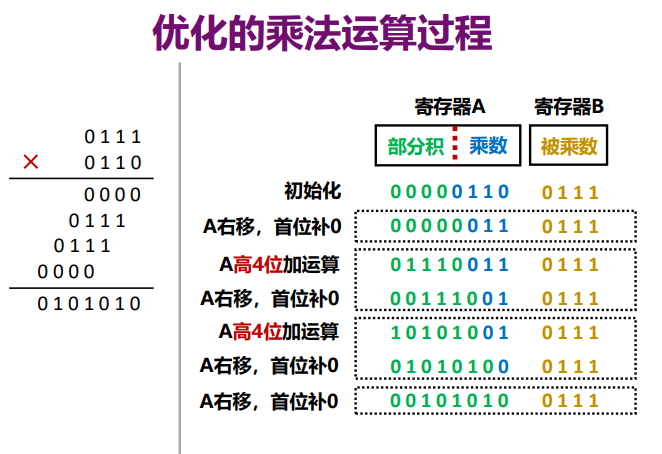

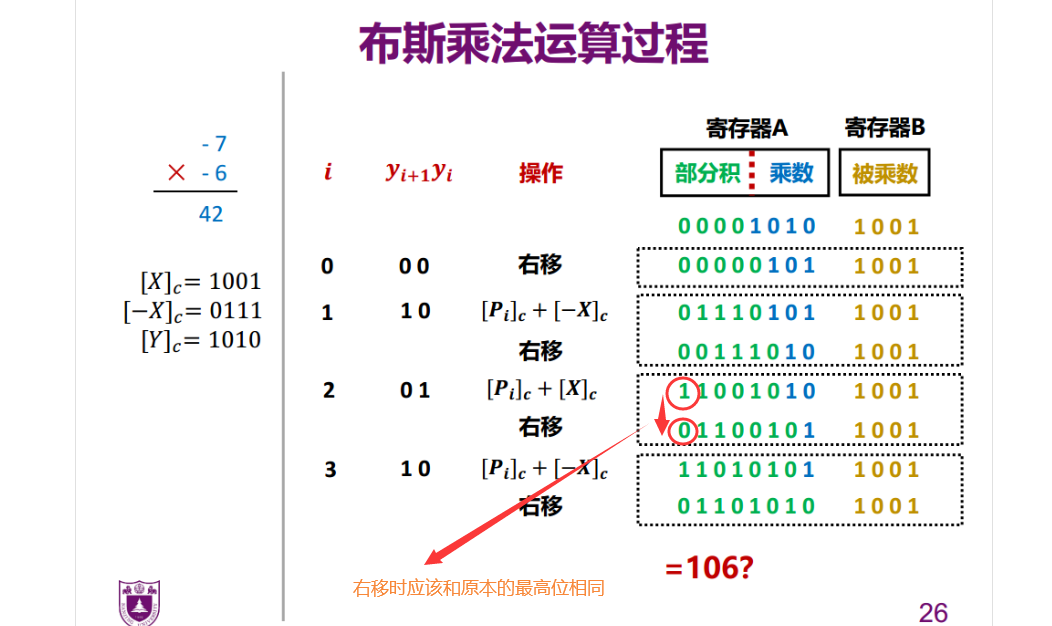

乘法

二进制乘法不需要乘法表进行存储。十分方便

优化

出错

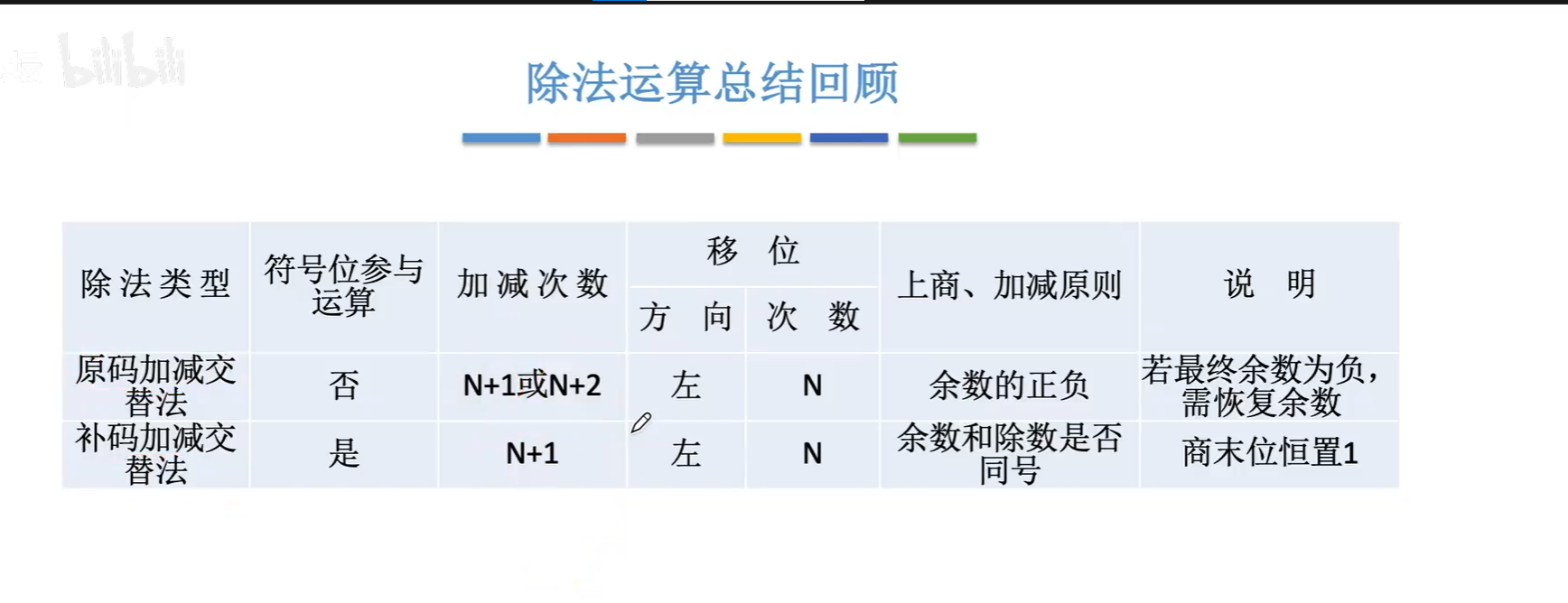

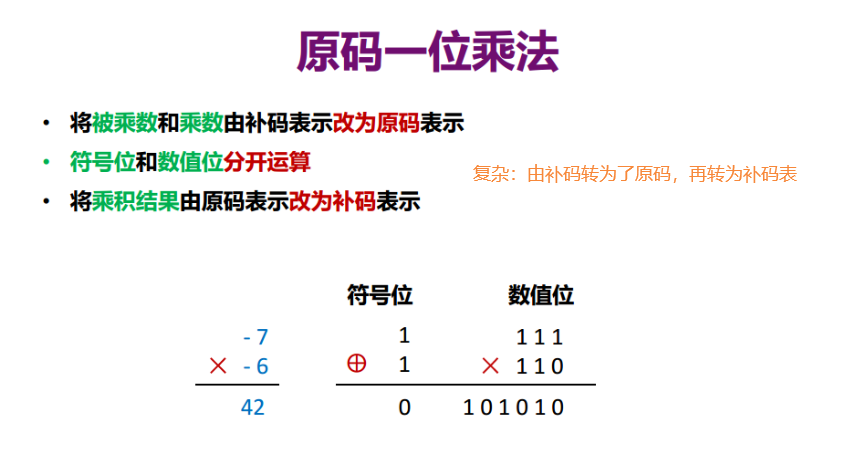

- 原码一位乘法

除法

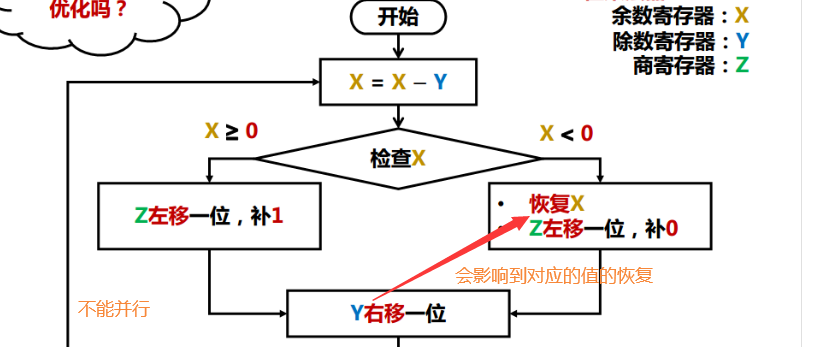

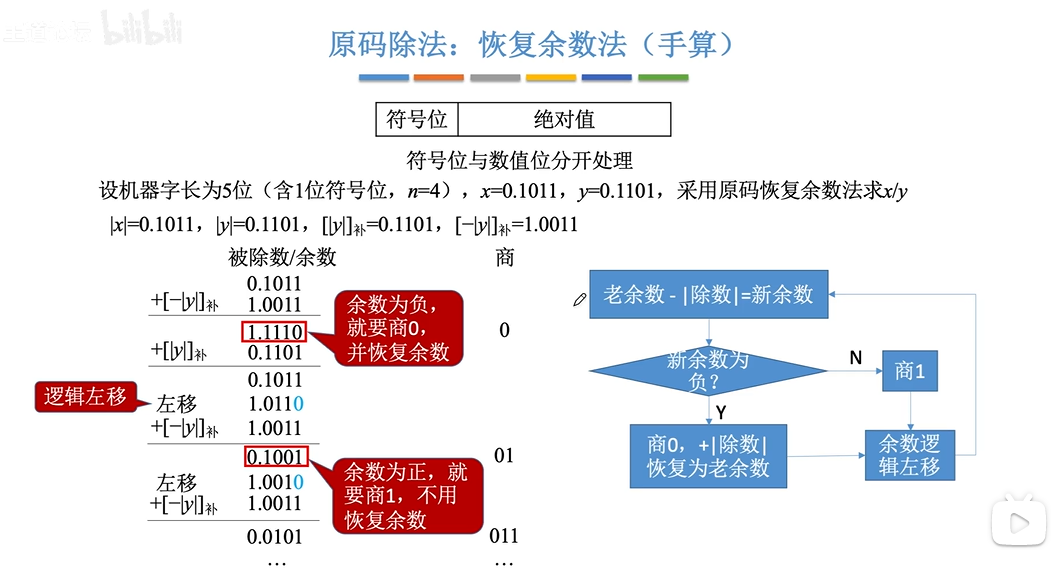

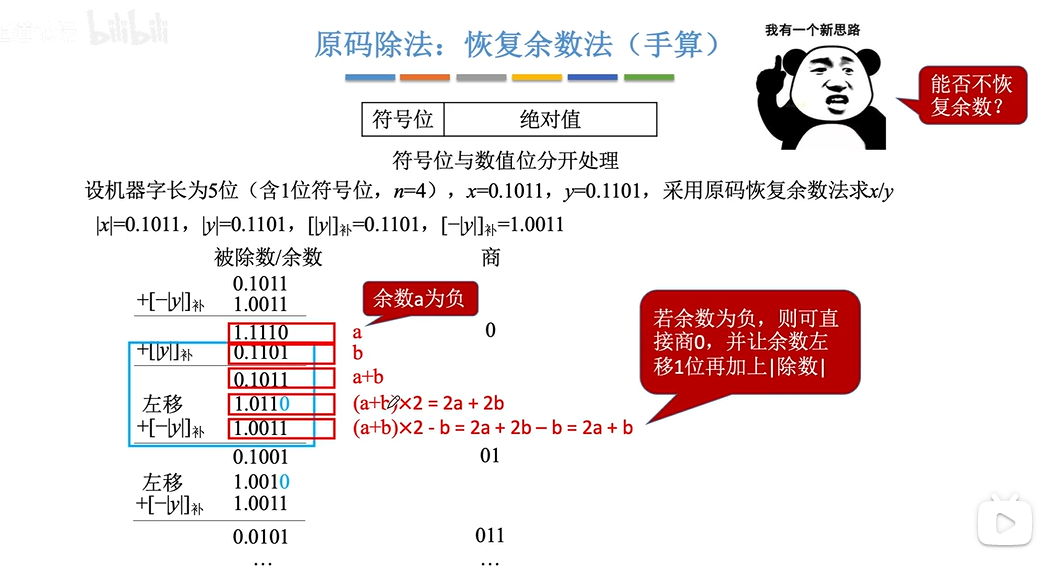

原码:恢复余数法

余数逻辑左移是为了实现错位相减。因为手算时实际上是除数右移,而我们规定除数不移动时,则是余数左移

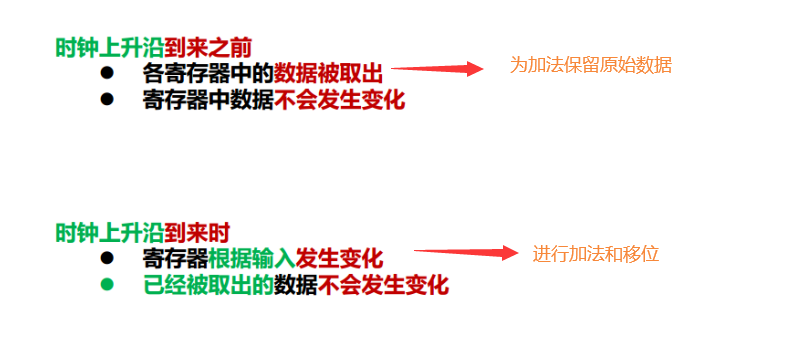

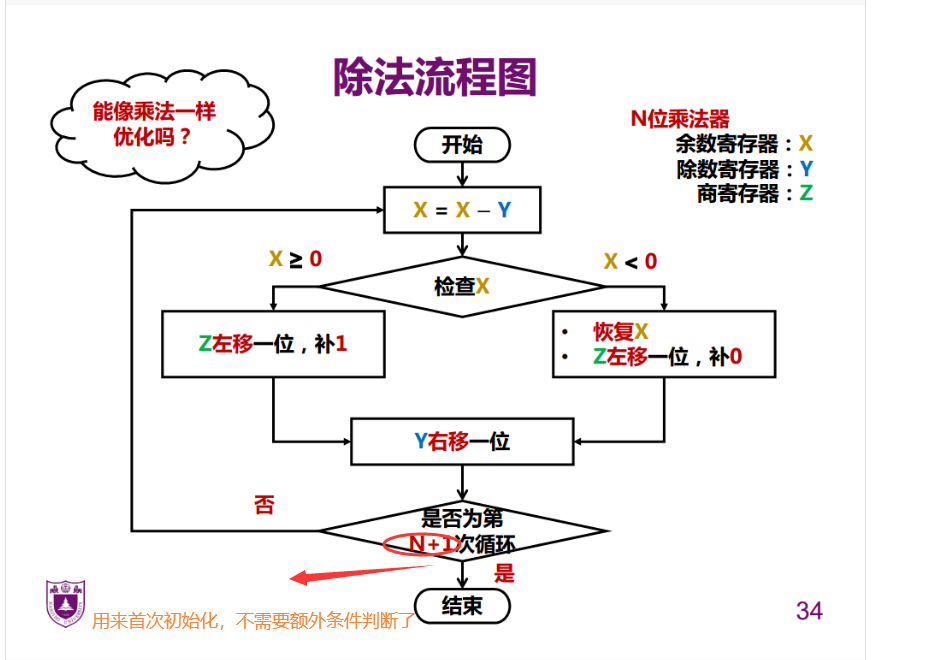

优化:并行+硬件的节省

并行:

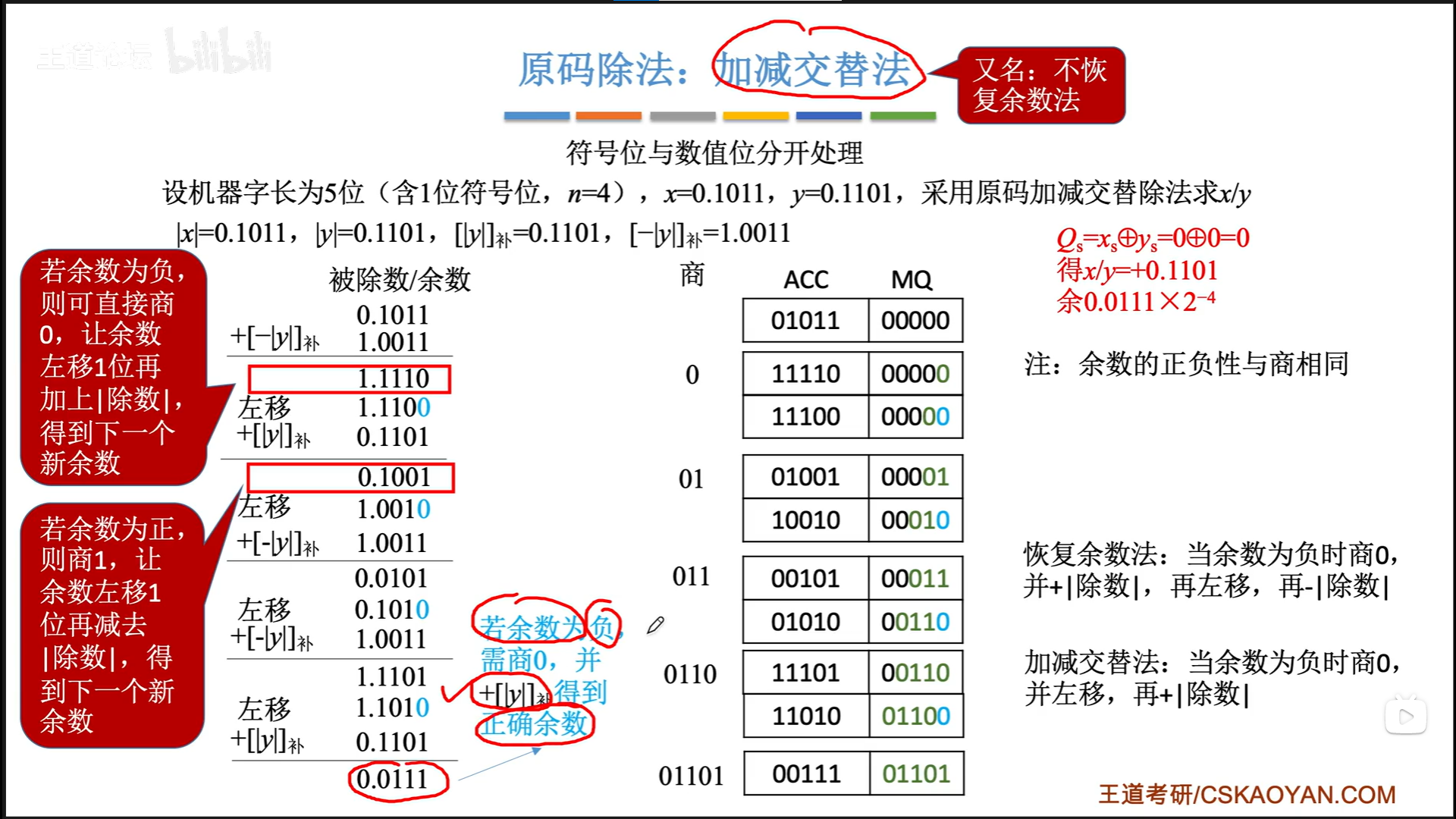

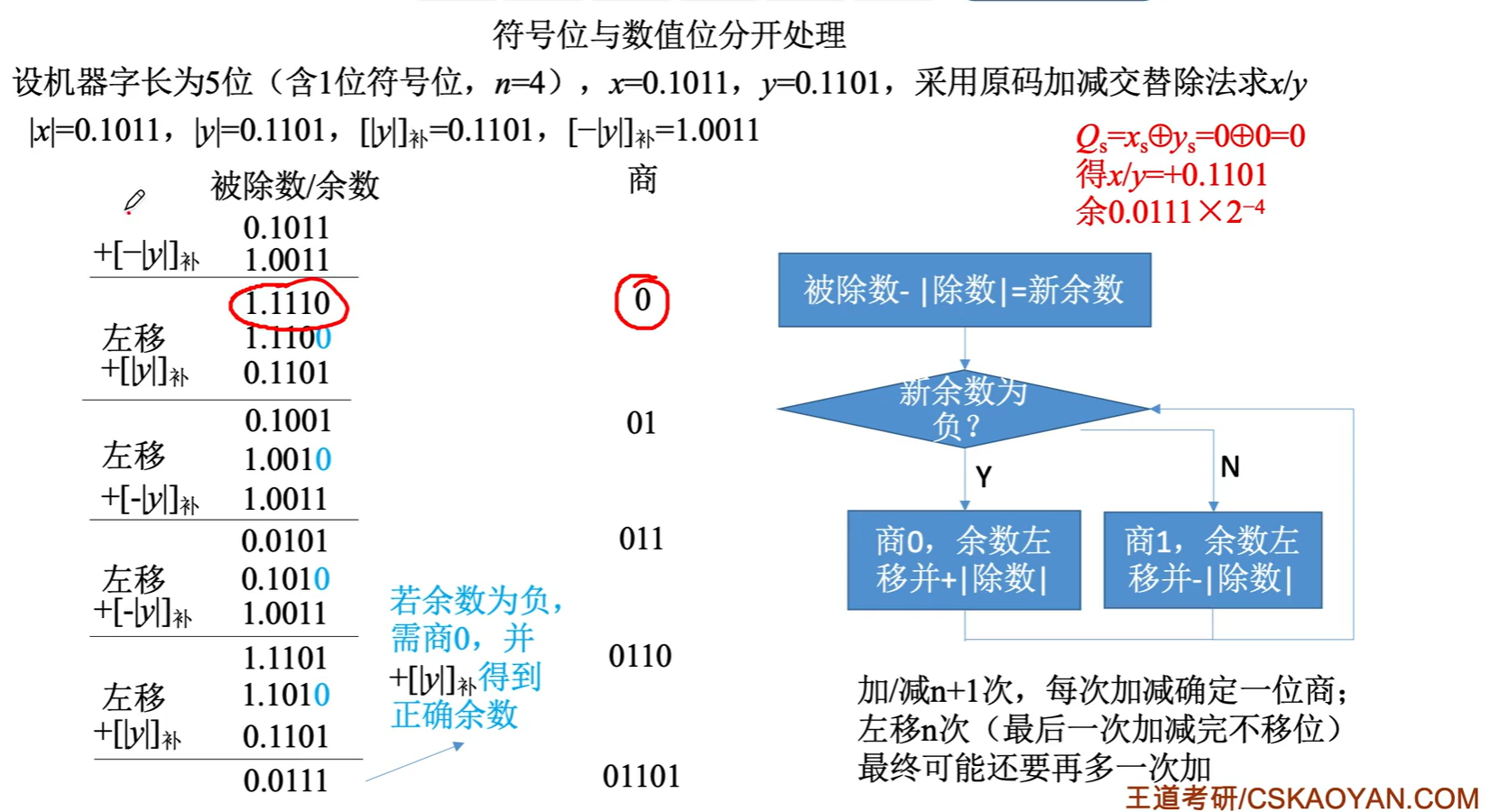

原码:不恢复余数法

若最后一步余数为负数,仍然需要恢复为正确余数

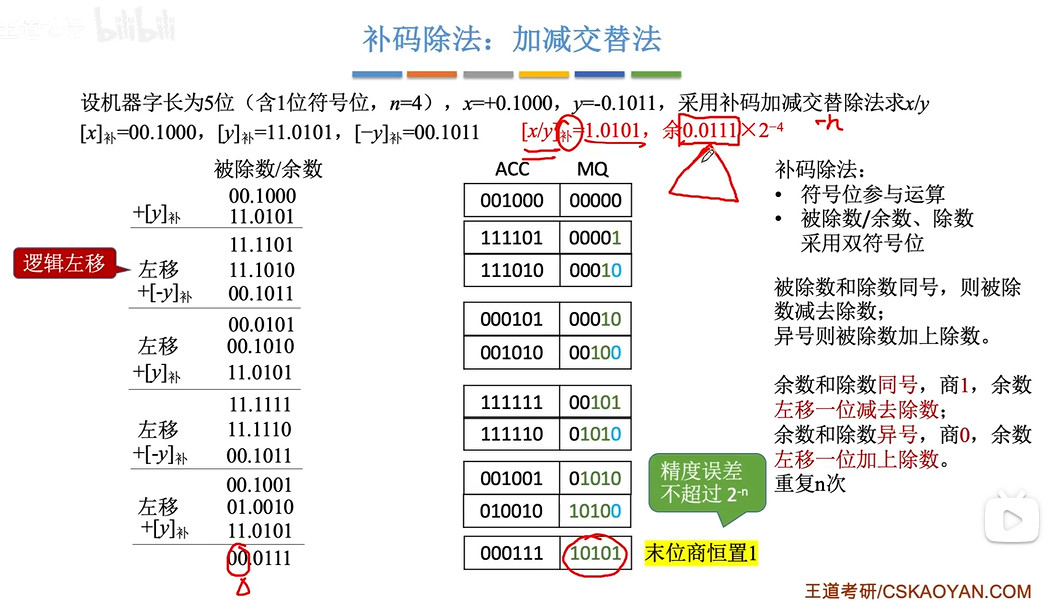

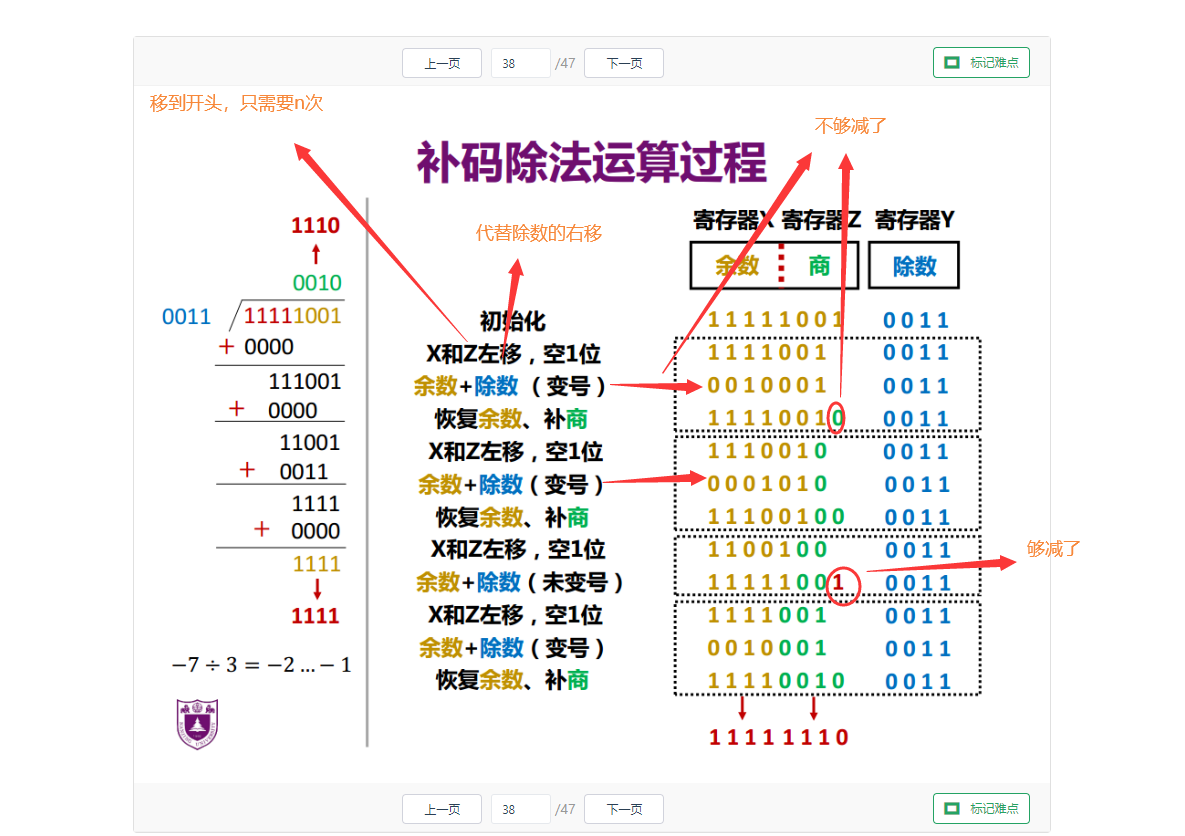

补码:不恢复余数法

余数和除数相减:

- 如果余数和除数的符号相同:减法

- 如果余数和除数的符号不同:加法

- 够减:余数和新余数的符号不能变

- 不够减:余数和新余数的符号改变

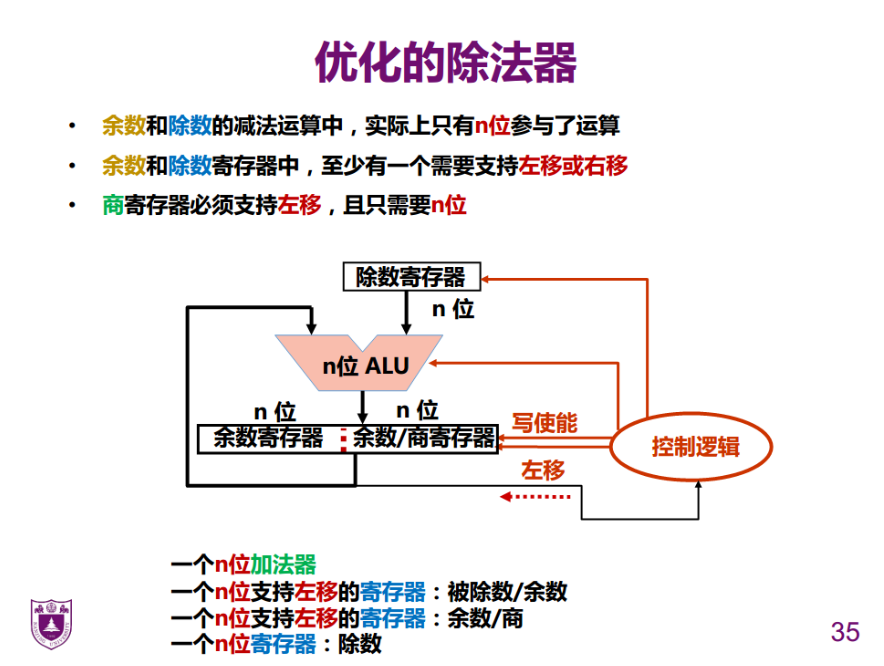

除法硬件改善

除法运算总结

溢出

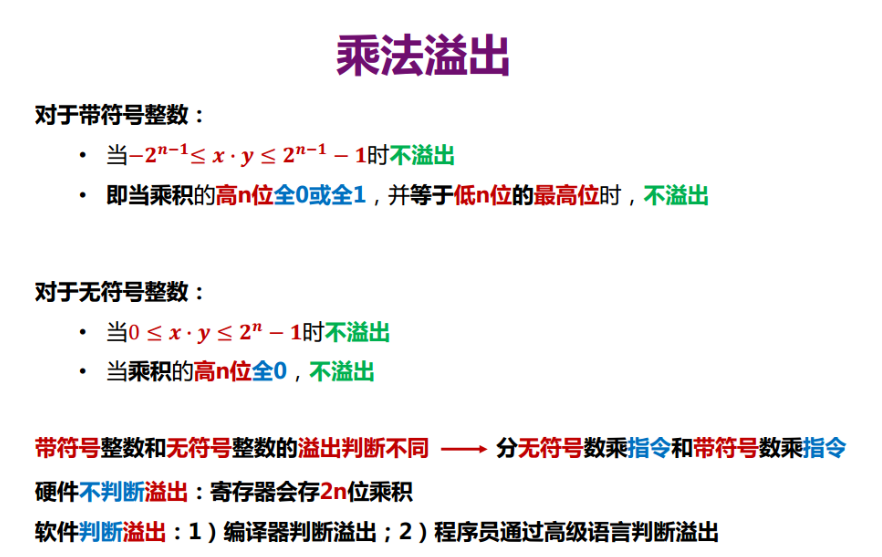

乘法溢出

本博客所有文章除特别声明外,均采用 CC BY-NC-SA 4.0 许可协议。转载请注明来自 丁丁的小窝(*^_^*)!