第十七课 输入输出

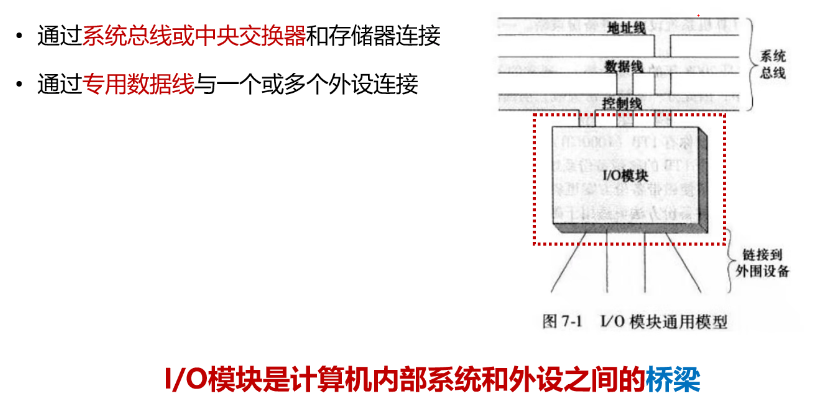

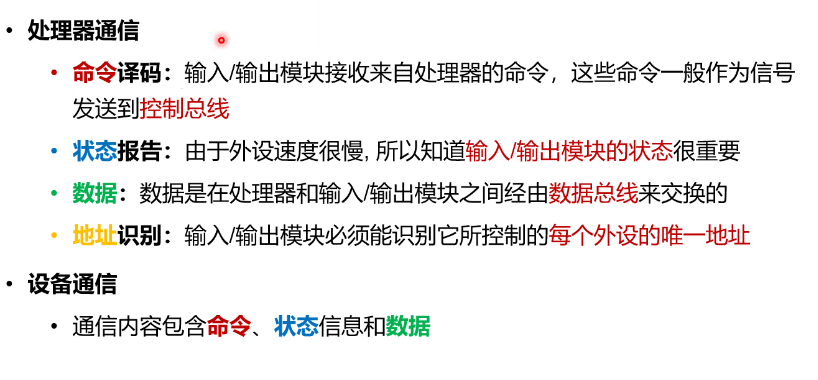

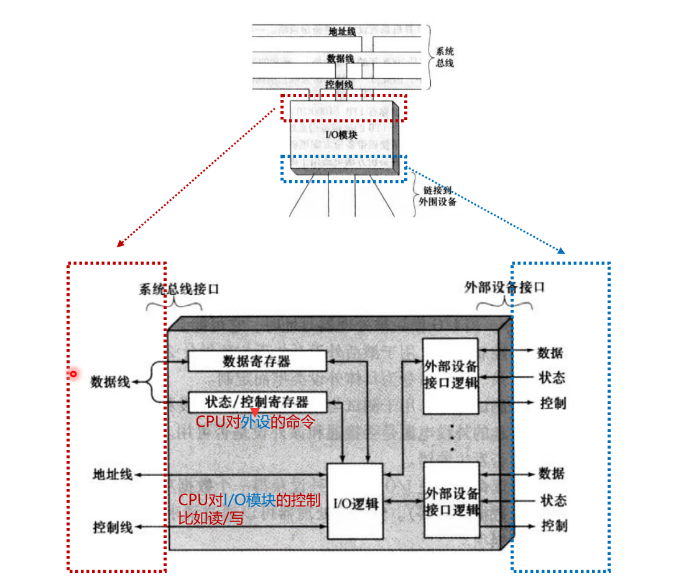

I/O模块

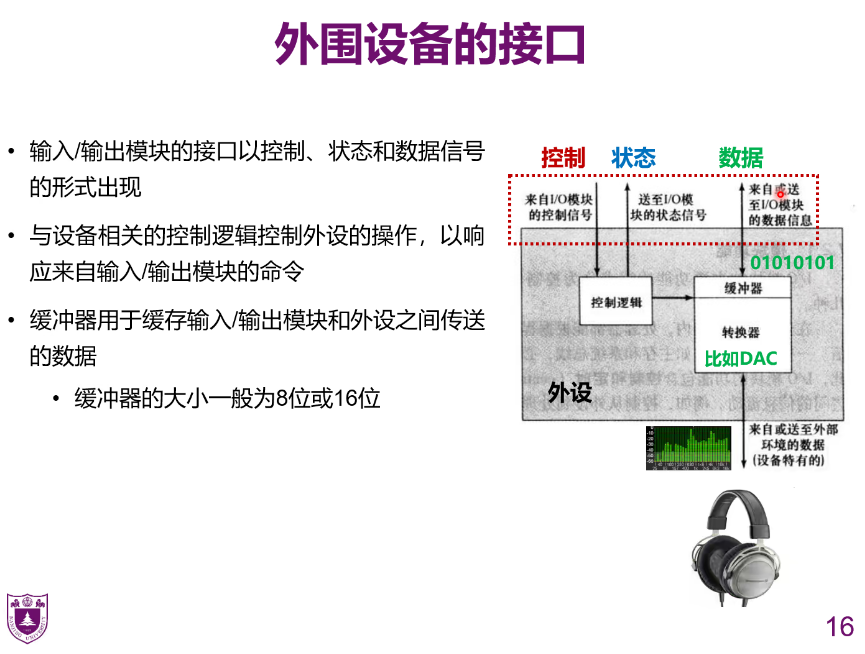

外围设备的接口

功能

结构

外部接口

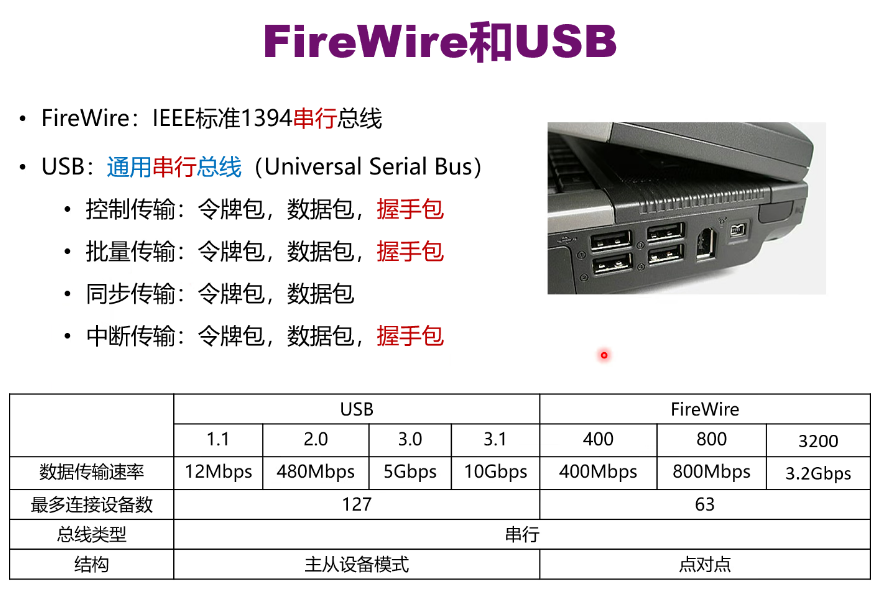

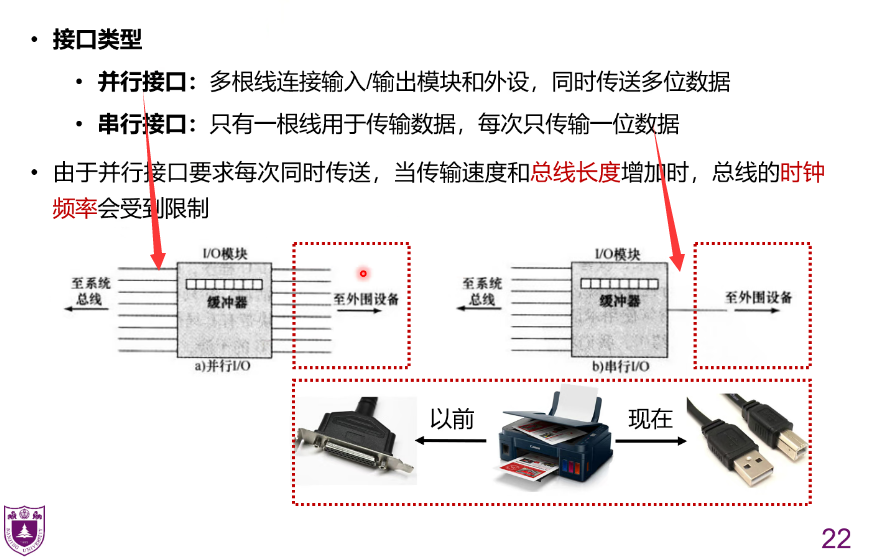

事实上,并行接口,每一根线的延迟可能是不一样的,当线的长度非常长时,每一位传输时就会导致错位,数据传输出错。

所以,需要按照一定频率传输

串行总线

- 批量传输比同步传输多了“握手”,是为了实现异步

- 同步传输:传送音视频时,需要同步。音视频对实时性的要求较高;允许一定的误码率

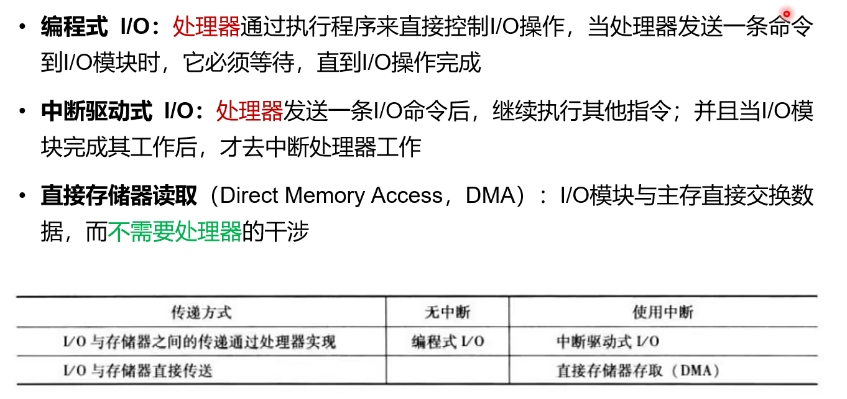

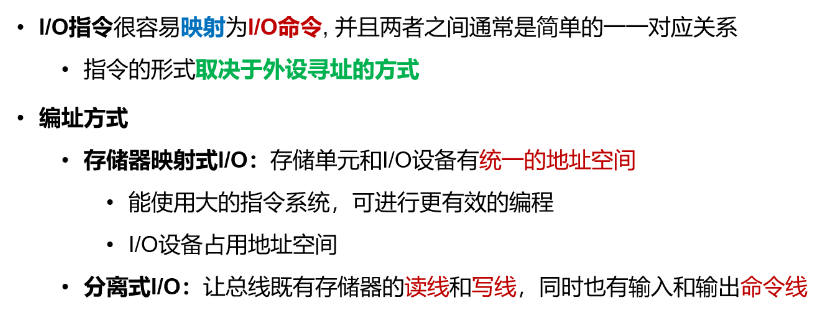

I/O操作技术

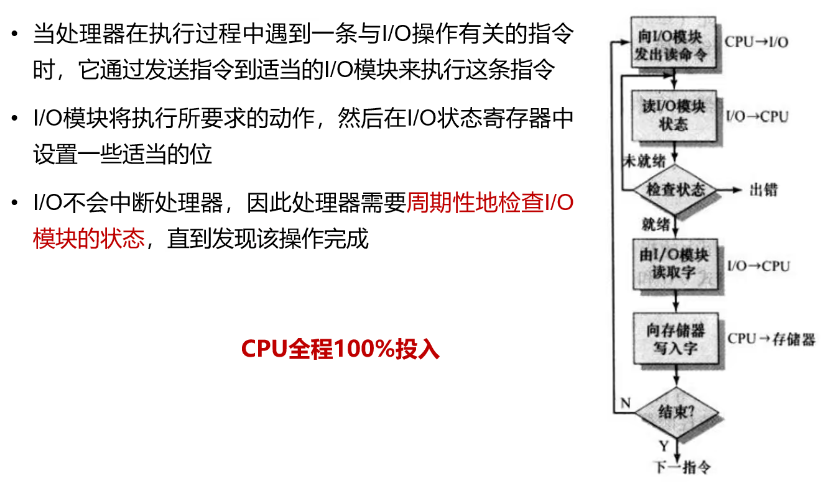

编程式I/O

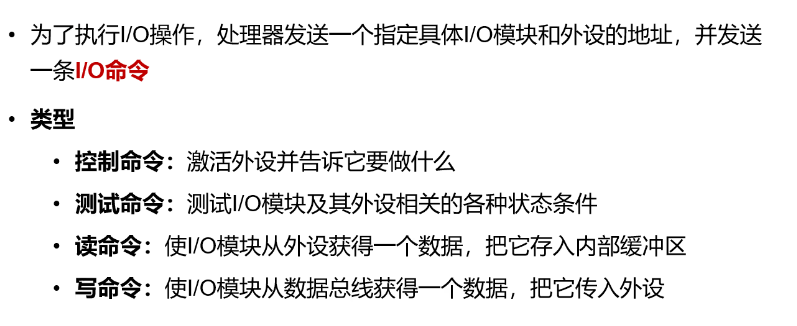

I/O命令

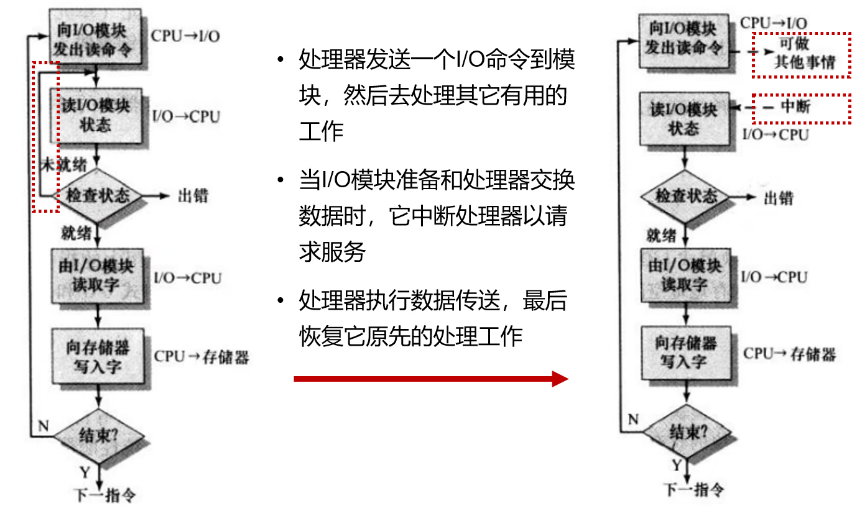

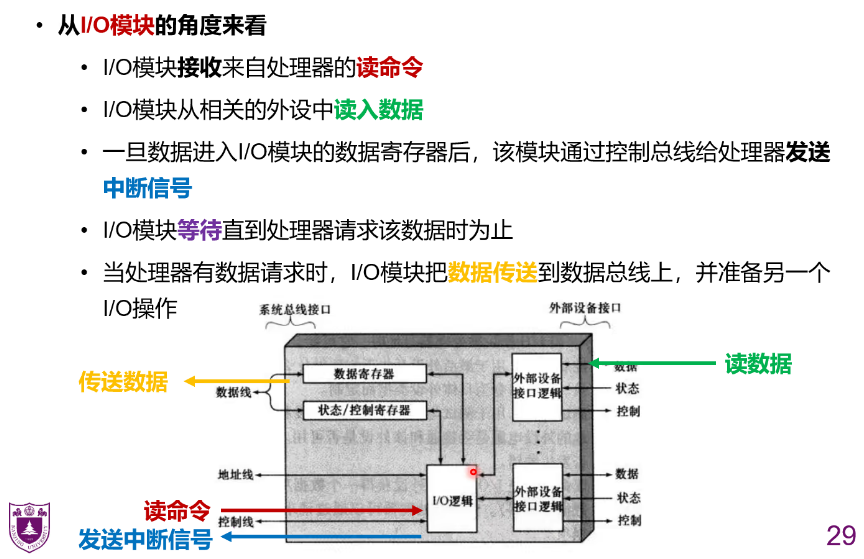

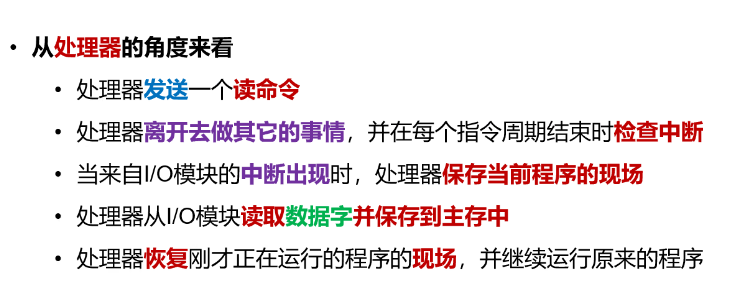

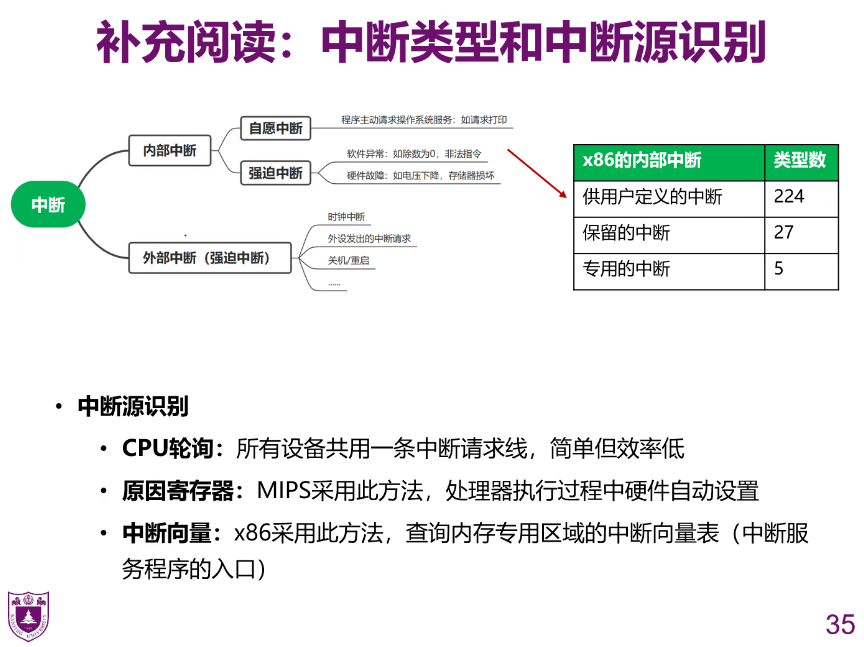

中断驱动式I/O

模块理解

- I/O模块等处理器,而不是处理器等I/O了

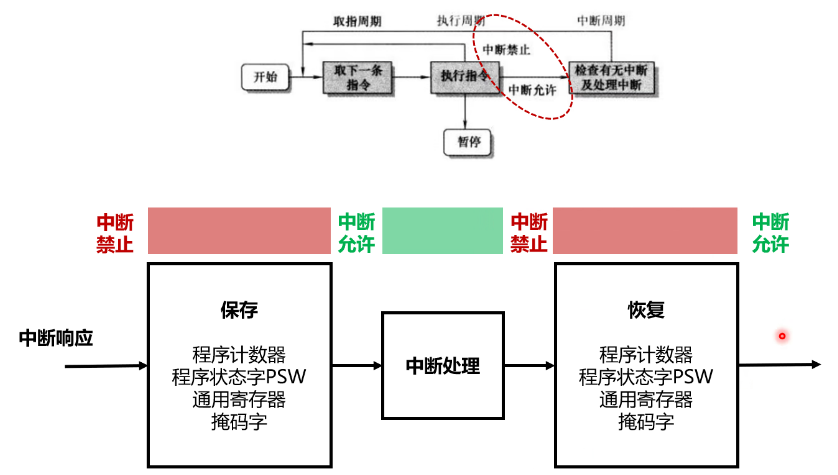

中断允许和中断禁止

- 中断处理之前,要保存现场

- 保存现场时,不能被中断。所以中断响应后,要进入中断禁止,保护现场

- 恢复现场时,也不能被中断

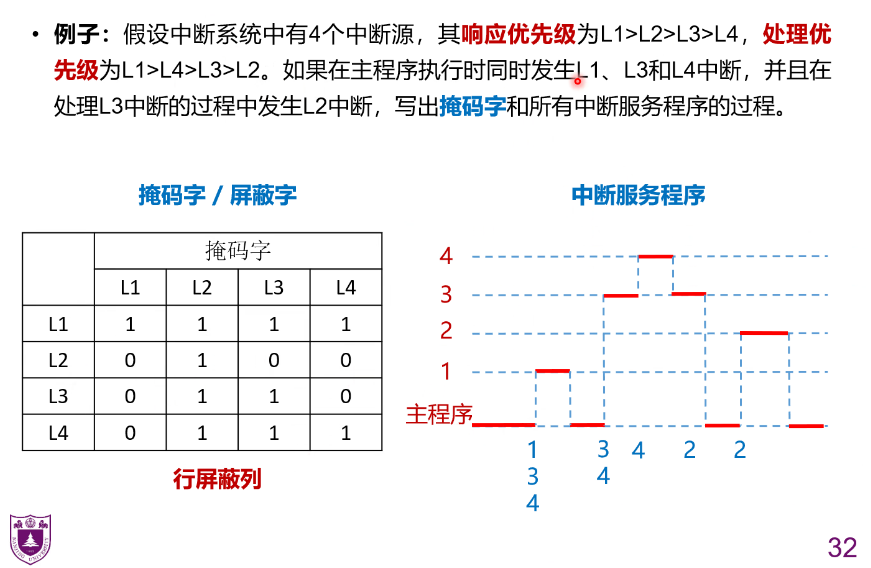

例题

- 主程序的响应优先级和处理优先级的最低

- 先执行和处理完L1(L3 L4的处理优先级比L1低),回到主程序

- 先响应3,但是先处理完L4

- 恢复L3,发生了L2中断,但是L2的处理优先级低于L3,所以先处理L3

处理优先级决定哪些中断可以被响应,响应优先级决定哪些中断最先被响应

行屏蔽是从处理优先级的角度出发的

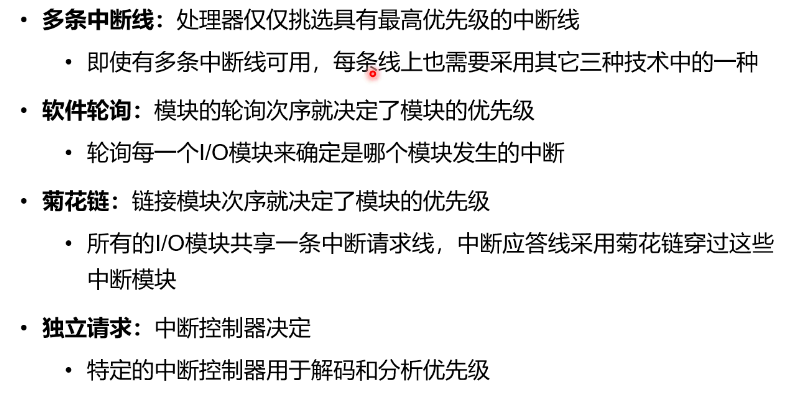

设备识别

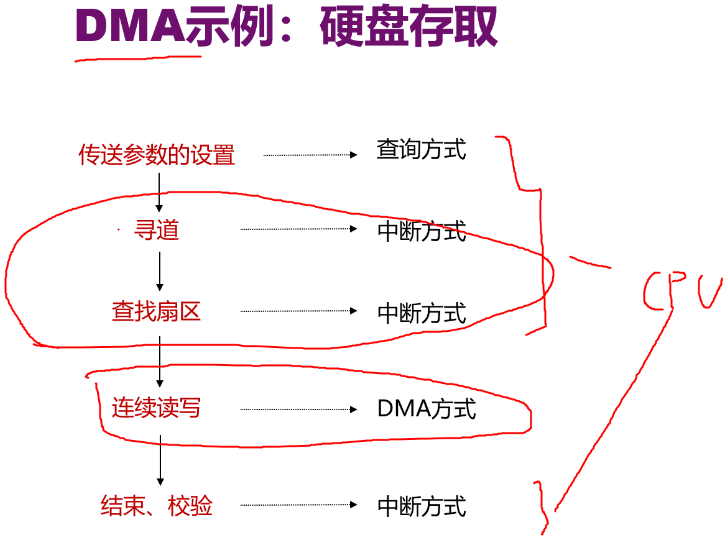

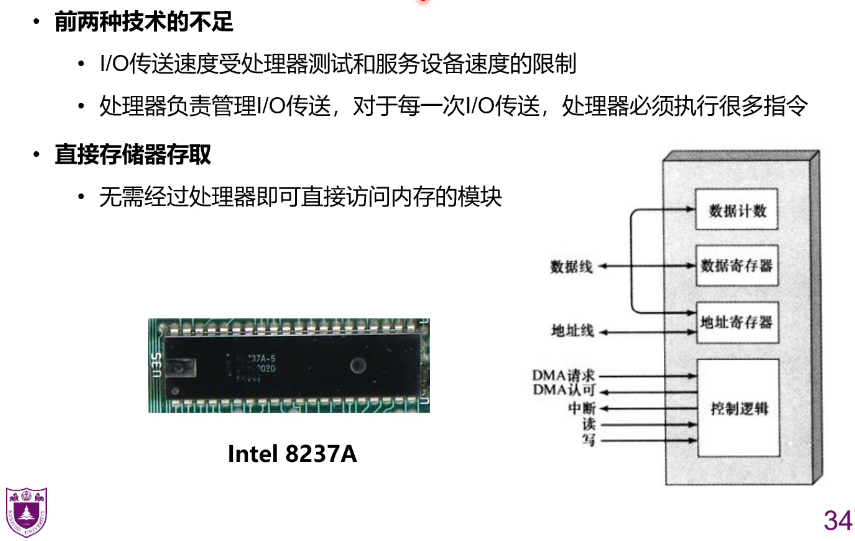

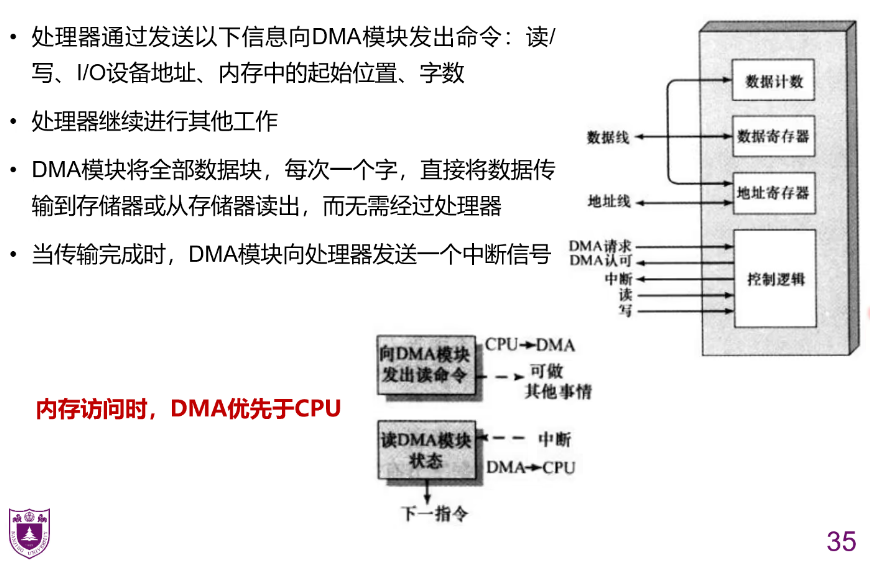

直接存储器存取 DMA

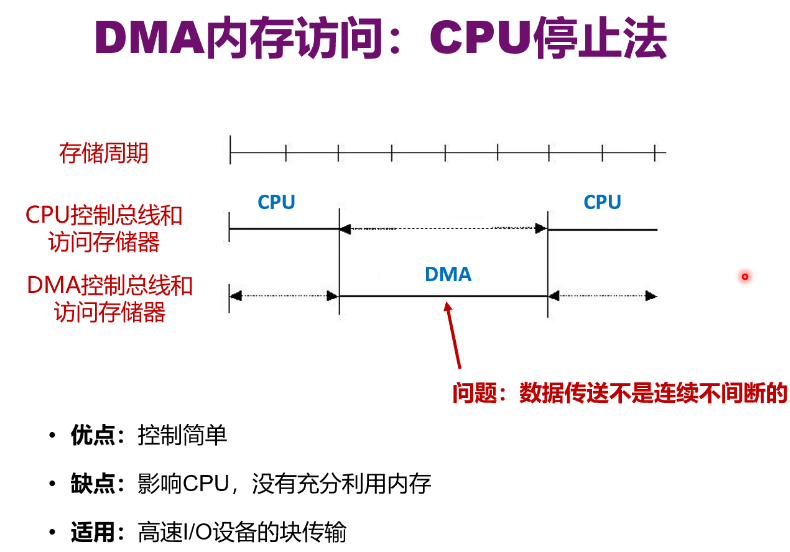

DMA内存访问:CPU停止法

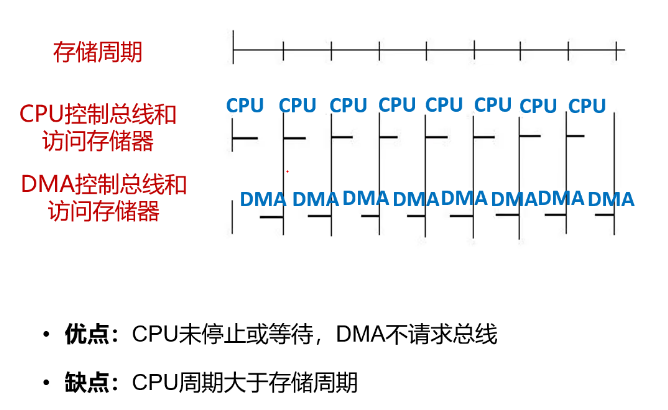

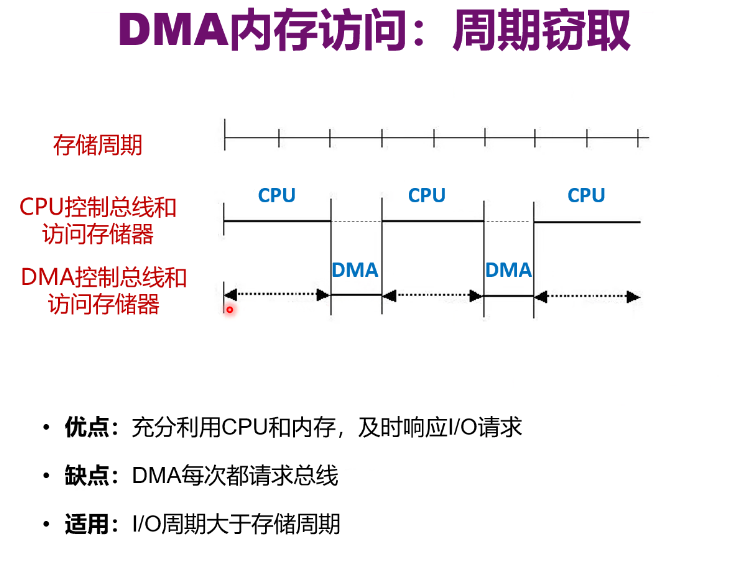

DMA内存访问:周期窃取

断断续续:存储周期处于空闲状态。一次IO请求可能会有多次DMA访存

DMA内存访问:交替分时访问

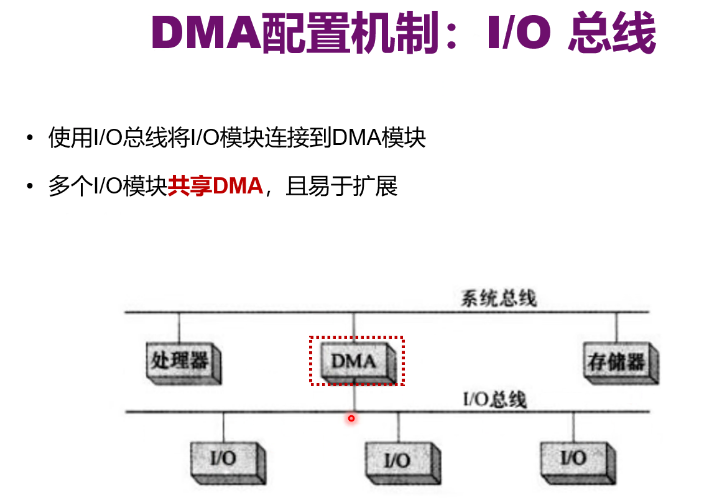

DMA配置机制:单总线分离DMA

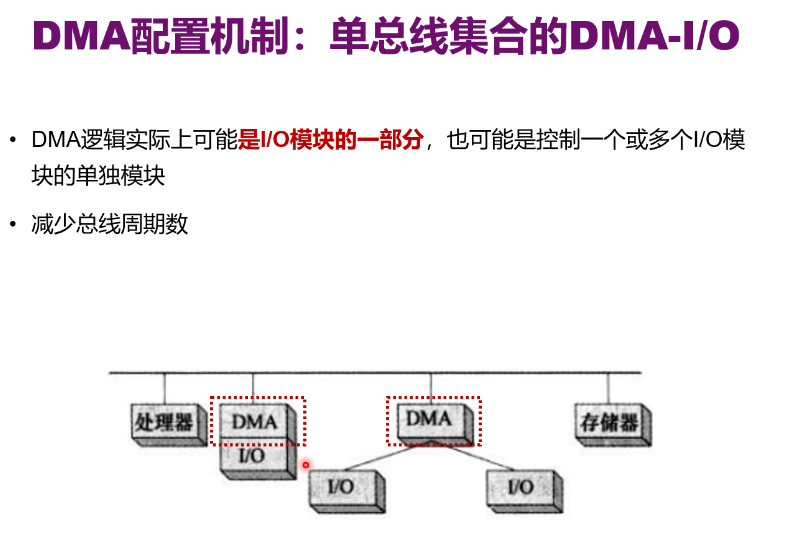

单总线集合的DMA

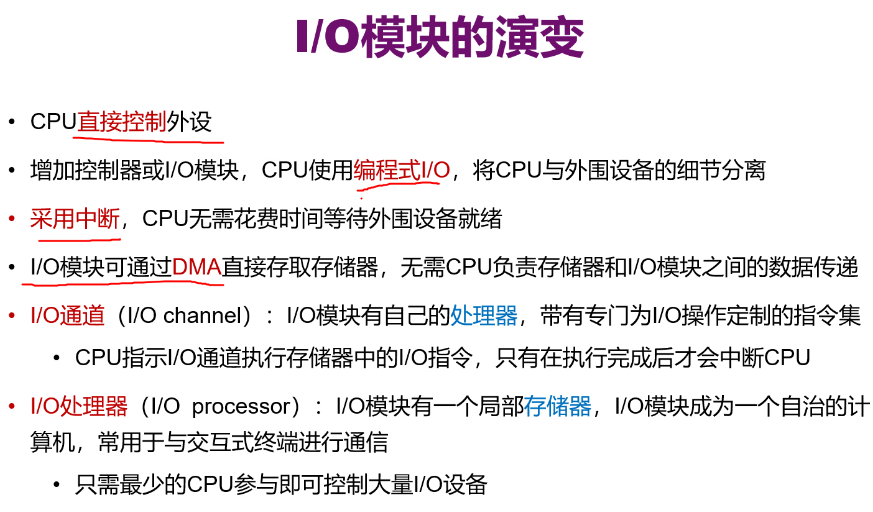

I/O模块的演变

I/O处理器不仅有处理器,同时也有了局部存储器

本博客所有文章除特别声明外,均采用 CC BY-NC-SA 4.0 许可协议。转载请注明来自 丁丁的小窝(*^_^*)!