第二课 计算机的顶层视图

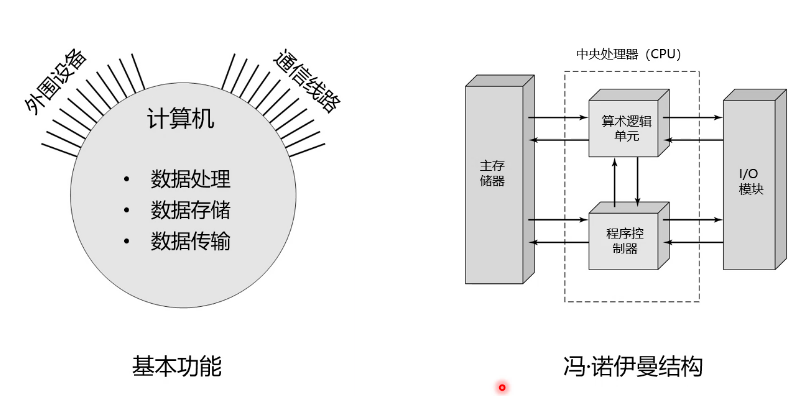

顶层设计:冯诺依曼结构=>计算机需要满足什么,具有一定的普适性。

第一台计算机:10进制

有反直觉的设计:2进制(最理想的进制是e)

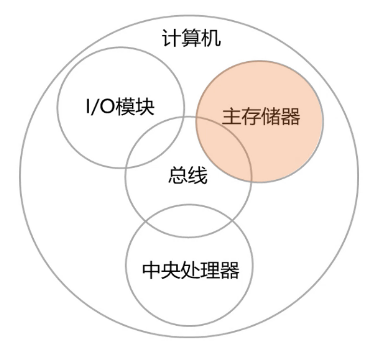

早期:组件之间用分散方式相连,现在主要用总线方式相连

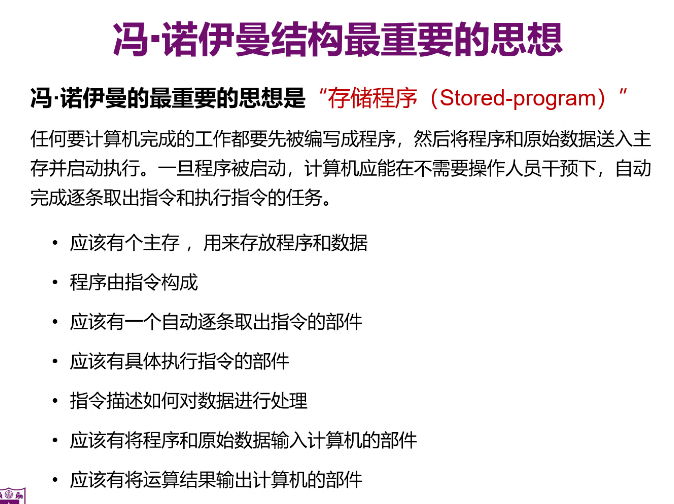

冯诺伊曼最重要的思想:**存储程序(Stored-program) **

ABC计算机是硬件编程,而不是软件编程,所以是专用计算机,而非通用计算机,不具有存储功能。

冯诺依曼结构将数据和程序存放在一起,而哈弗结构将两者分开。有一些ARM(Cortex-M系列)是哈佛结构,而另一些ARM(Cortex-A)是冯诺依曼结构

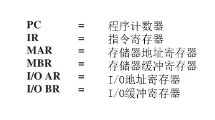

关键概念:

- 指令和数据存储在单个读写存储器中

- 主存中的内容按位置访问,无需考虑其中包含的类型

- CPU从一条指令到下一条指令以顺序方式执行(除非明确修改)

- 与CPU和内存交换从外部来源收集的数据

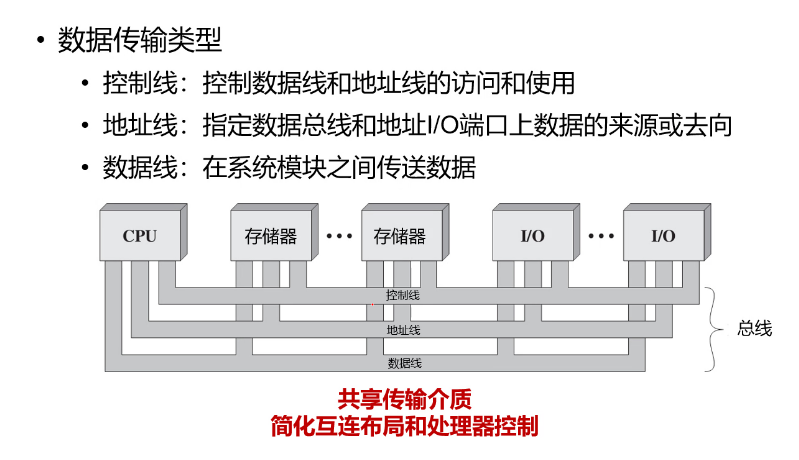

- 总线是连接两个或多个设备的通信通路

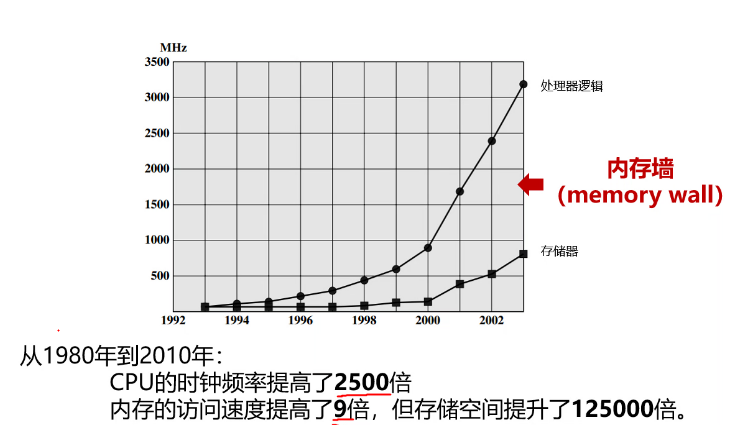

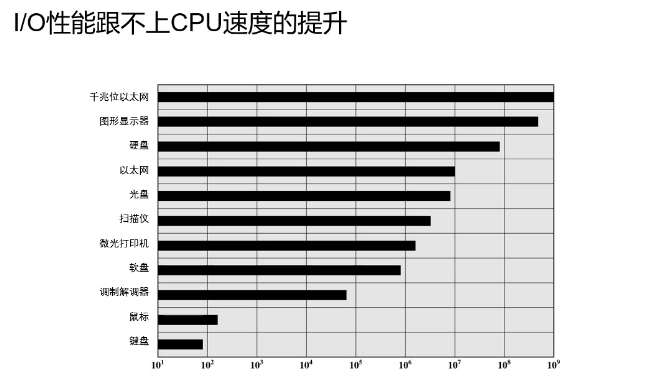

不成比例扩展效应:计算机各个部分的发展是不同步的。目前CPU的发展速度远远快于存储,会出现速度匹配不一致的影响

CPU

相关概念

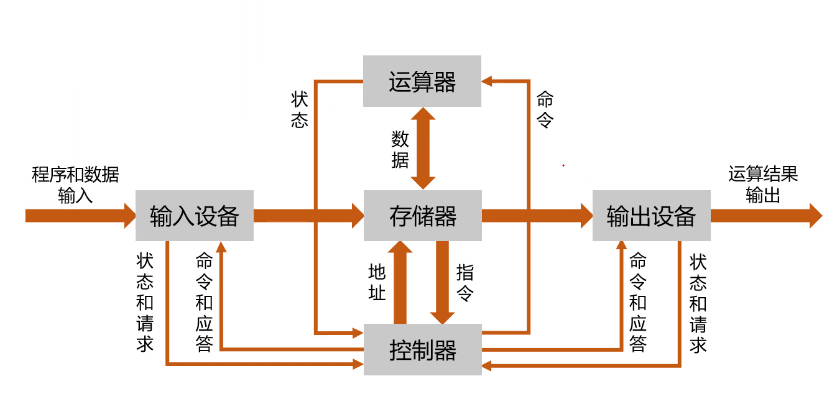

中央处理单元/中央处理器 定义:获取并执行指令的计算机组成部分。由一个ALU、一个控制单元和多个寄存器构成。

处理器 processor:含有一个或者多个内核的物理硅片。处理器是计算机组件,用于解释和执行指令。如果一个处理器包含多个内核,则称之为多核处理器 (此处定义并不精准)

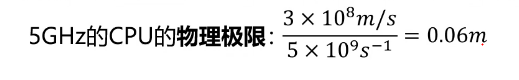

随着时代的发展,CPU的大小几乎不变,晶体管的数量一直增加,但是有一个物理极限。每个晶体管都可以看成一个开关,传输和开关都需要时间

无限增大CPU的面积=>面积增大,代表着互连延迟增大。一个时钟周期需要大于最大互联延迟

CPU相关问题

问题1:CPU的频率不能无限提高

- 理论限制

- MOS管开关、脉冲通过门电路需要时间

- 为了信号同步,每个脉冲信号需要持续一定的时间

- 制造限制

- 芯片面积越来越大,导致连线延迟越来越大,需要保证信号在设计指定时钟周期内从芯片的一角到达另一角

- 频率越高(即MOS管的开关频率也越高)会导致开关(电能状态变化)损耗也越高,CPU耗电和散热会提高。Mac book air(无风扇,CPU频率低)<Mac boor pro(有风扇)

必须在其他条件限制下,才能说频率越高性能越好

解决方法:改进CPU芯片结构+领域定制,面向特定领域开发芯片

晶体管数量的增加为更先进、更复杂的体系结构提供了基础

问题2:内存墙的存在

主存和CPU之间传输数据的速度跟不上CPU的速度

对于CPU:希望速度变快

对于内存:希望存储空间变大

解决方法:采用高速缓存(Cache)— 和缓存进行交互,

- 增加一级或多级缓存,以减少存储器访问频率并提高数据传输速率

- 增大总线的数据宽度,来增加每次所能取出的位数

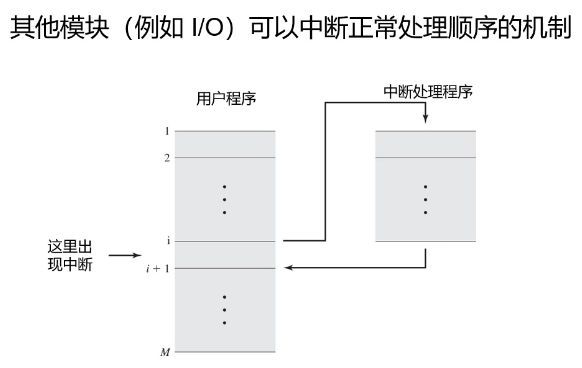

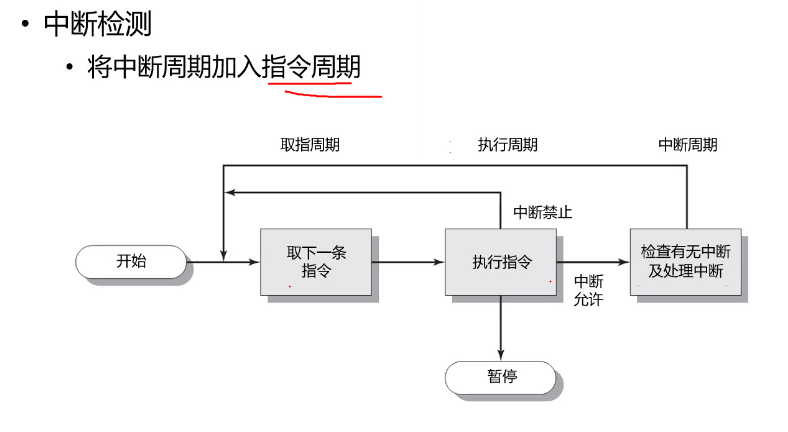

问题3:CPU等待I/O传输数据

CPU在等待I/O设备时保持空闲

解决方法:采用中断机制

中断:

多重中断:

- 多个中断处理顺序排列(无优先级)

- 多个中断处理嵌套排列(有优先级)

存储器

CPU中的存储器

问题

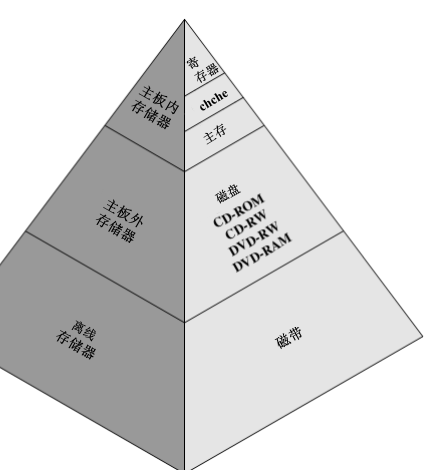

兼容存储容量、速度和成本

约束:

- 容量:越大越好

- 速度:跟上处理器

- 成本:相对于其他组件合理,难以做到又大又快

约束之间的关系:更短的访问时间,更高的每比特成本

解决:层次式存储结构

从上往下:

- 数量越来越大

- 速度越来越慢

- 离CPU越来越远

主板外存储器 -> I/O设备(外围设备,类似于鼠标、键盘)

CD:光驱读取

离线存储器:磁带(纪录片拍摄曾用)

需求

- 大容量数据存储

- 高速性能

I/O模块

与CPU和内存交换从外部来源收集的数据

I/O设备不是I/O模块

问题:I/O设备传输速率差异大

- CPU和内存速度不匹配:Cache -> CPU必须直接和内存交换

- CPU和I/O设备:采用中断机制 -> CPU可以和内存交换

解决:

总线

两大基本特征:

- 共享:多个部件连接在同一组总线上

- 分时:同一时刻,总线上只能传输一个部件发送的信息

问题:计算机部件互连复杂

解决:采用总线

总结