第七课 存储器

定义

存储器(Memory )由一定数量的单元【一个单元往往存储的是一个字节】构成,每个单元可以被唯一标识,每个单元都有存储一个数值的能力

- 址:单元的唯一标识符(采用二进制)

- 地址空间:可唯一标识的单元总数

寻址能力∶存储在每个单元中的信息的位数,即内存中能被单独识别并独立存放一个数据的最小内存空间

- 大多数存储器是字节(8bit )寻址的,32位计算机的最大寻址空间为4GB。

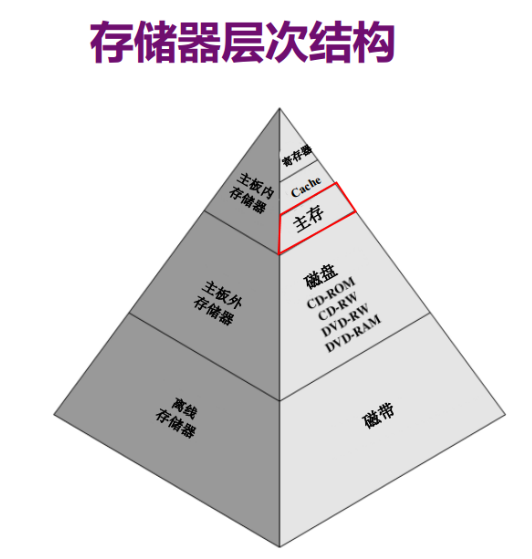

存储器层次结构

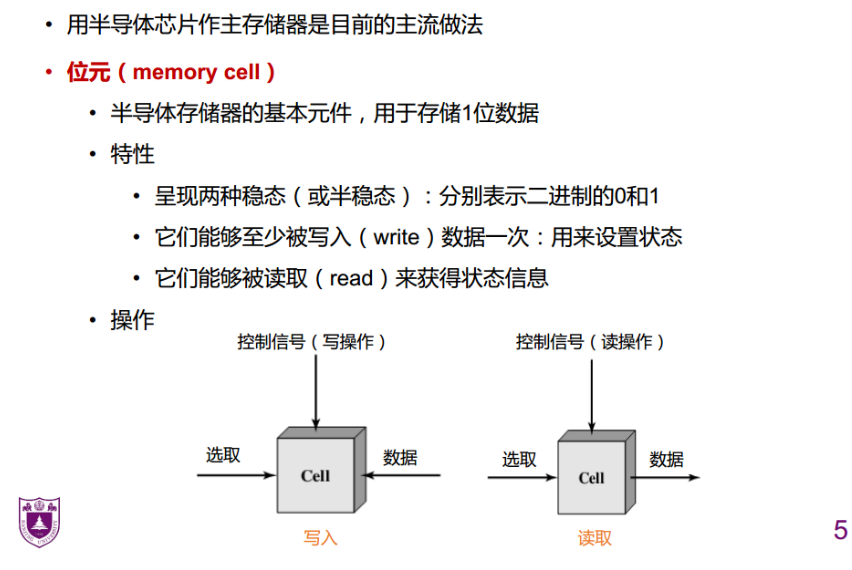

半导体存储器

- 双稳态:没有外部信号,会保持目前所处的状态

- 单稳态:只能处于一种状态,给予一种刺激由0变为1后,会慢慢变为0 – 类似弹簧

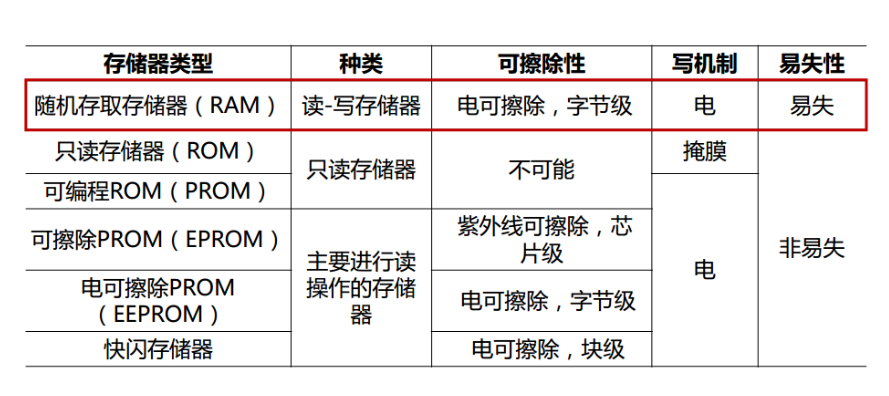

类型

介质:半导体

读写存储器

随机存取存储器 RAM

- 反面:顺序存储器-磁带。需要倒带到特定顺序才能播放

- 随机不是代表位置的存取是随机的,而是代表时间是相同的

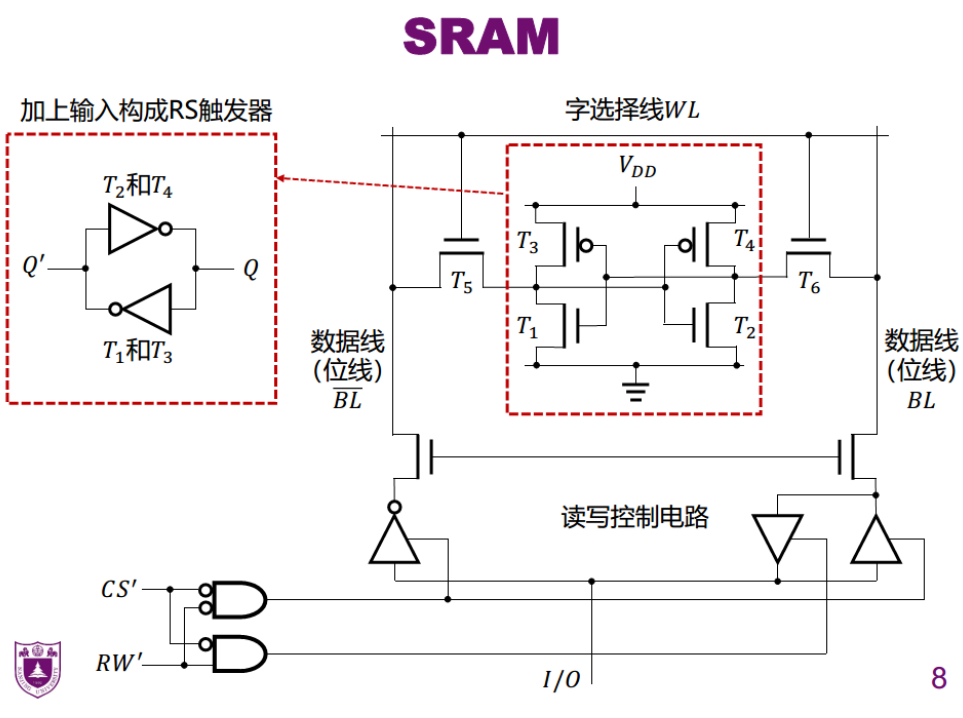

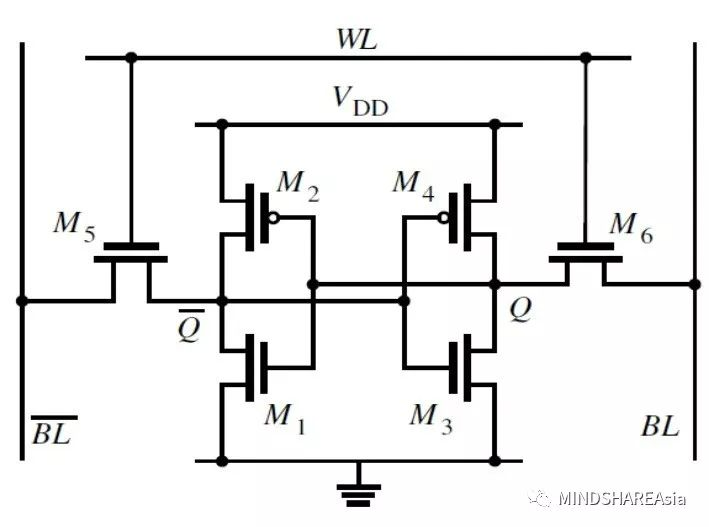

SRAM

写0操作

写0的时候,首先将BL输入0电平,(~BL)输入1电平。

然后,相应的Word Line(WL)选通,则M5和M6将会被打开。

0电平(来自BL)输入到M1和M2的G极控制端

1电平(来自~BL)输入到M3和M4的G极控制端

因为M2是P型管,高电平截止,低电平导通。而M1则相反,高电平导通,低电平截止。

所以在0电平的作用下,M1将截止,M2将打开。(~Q)点将会稳定在高电平。

同样,M3和M4的控制端将会输入高电平,因NP管不同,M3将会导通,而M4将会截止。Q点将会稳定在低电平0。

最后,关闭M5和M6,内部M1,M2,M3和M4处在稳定状态,一个bit为0的数据就被锁存住了。

此时,在外部VDD不断电的情况下,这个内容将会一直保持。

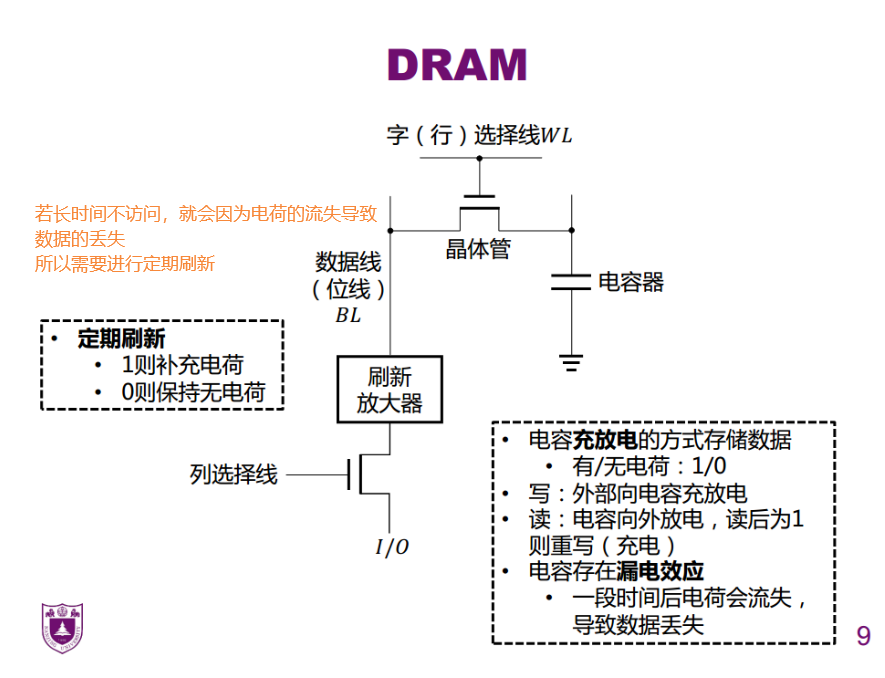

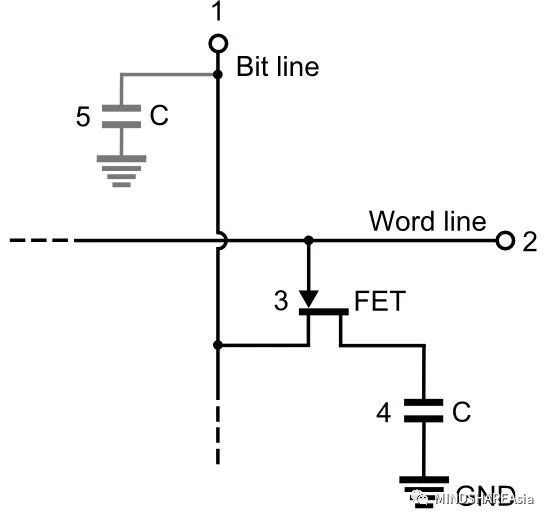

DRAM

其写操作相对简单:(我们以写1为例)

当需要写1的时候,先将BL(Bit Line)输入高电平1,然后选中对应的Word Line(同一时间将只有一根WL被选中), 打开相应的MOS管,如图中所示3号位。此时,外部驱动能力很强,通过一定的时间,4号位的电容将会被充满。此时,关闭3号位的MOS管。内容1将在一定时间内被保存在4号位的电容中。写0的操作与之相反,不同的是将4号位电容中的电荷通过Bit Line放光。然后关闭3号位的MOS管,锁存相应数据。

而读操作相对来说,较为复杂。我们可以观察到4号位电容非常小,只有pF级别,而Bit Line往往都很长,上面挂了非常多个存储单元(cell),我们可以通过5号位的电容来表示。所以当我们直接把3号位的MOS管打开,Bit Line上将基本看不到什么变化,所以需要刷新放大器

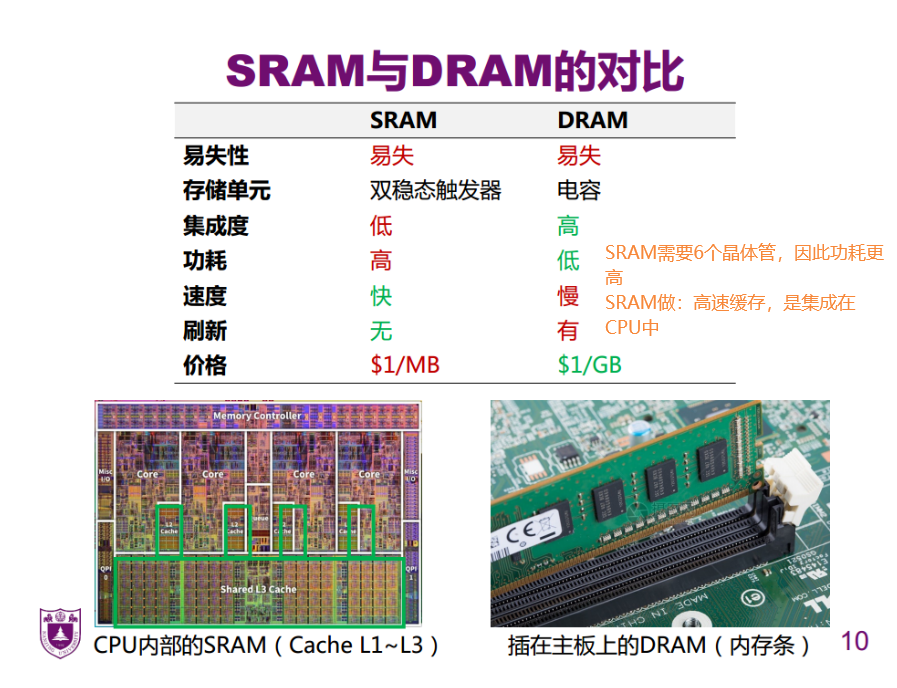

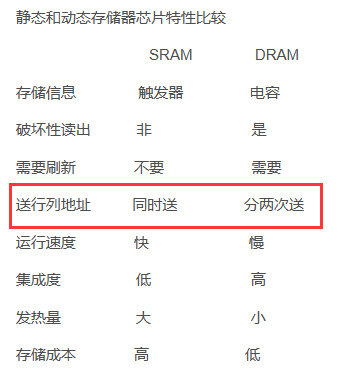

对比

SRAM和DRAM的区别

- SRAM成本比较高(6 个场效应管组成一个存储单元)DRAM成本较低(1个场效应管加一个电容)

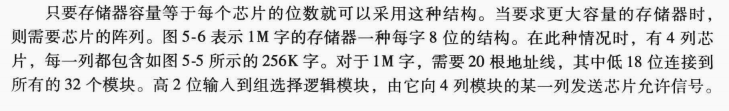

- SRAM存取速度比较快 DRAM存取速度较慢(电容充放电时间)

- SRAM一般用在高速缓存中 DRAM一般用在内存条里

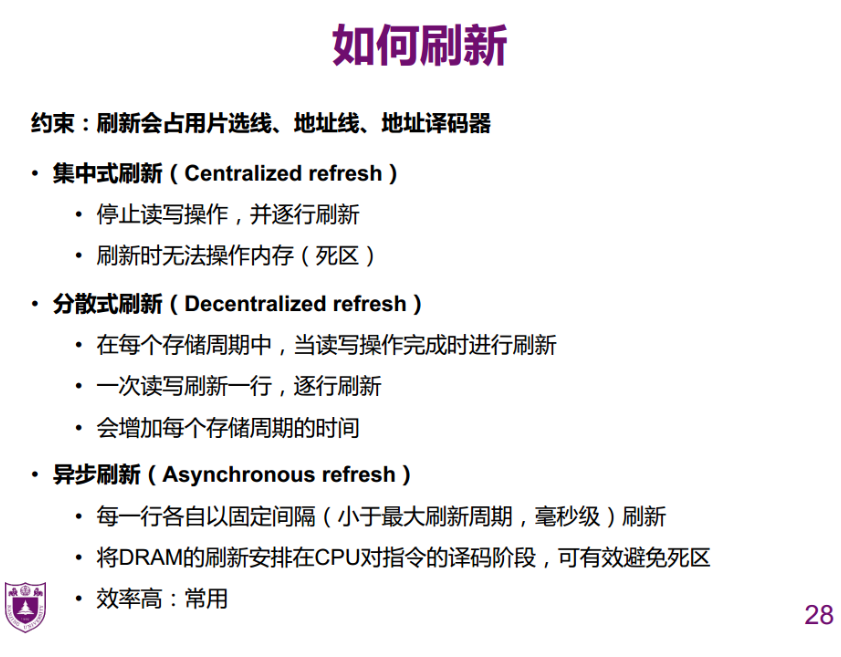

动态存储器的定期刷新:在不进行读写操作时,DRAM 存储器的各单元处于断电状态,由于漏电的存在,保存在电容CS 上的电荷会慢慢地漏掉,为此必须定时予以补充,称为刷新操作

只读存储器

只读存储器 ROM

可编程ROM (PROM)

主要读的存储器

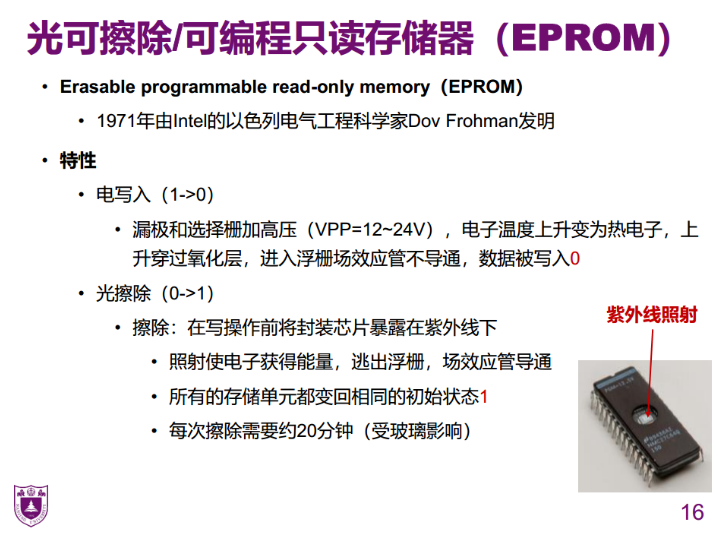

EPROM

缺点:

- 不精准。芯片级的擦除,一次照射,所有的位元都会清除。

- 擦除时间受玻璃材质影响大

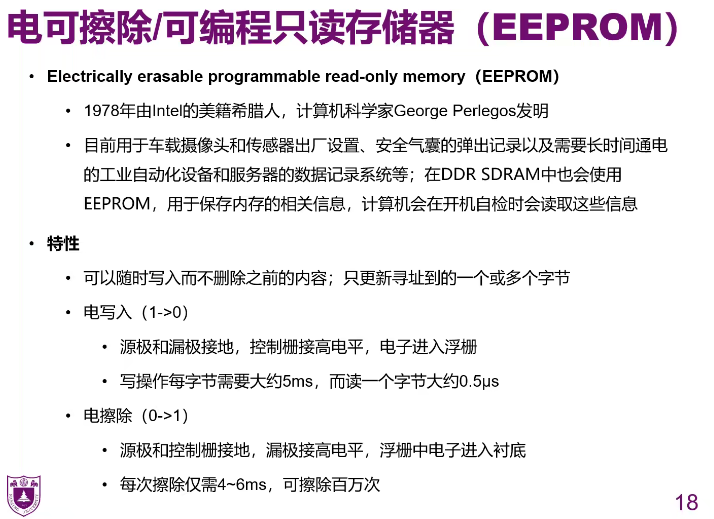

EEPROM

快闪存储器

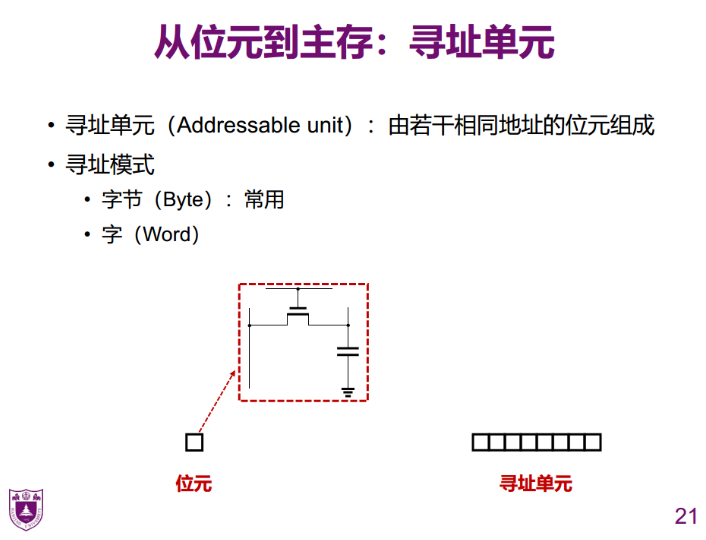

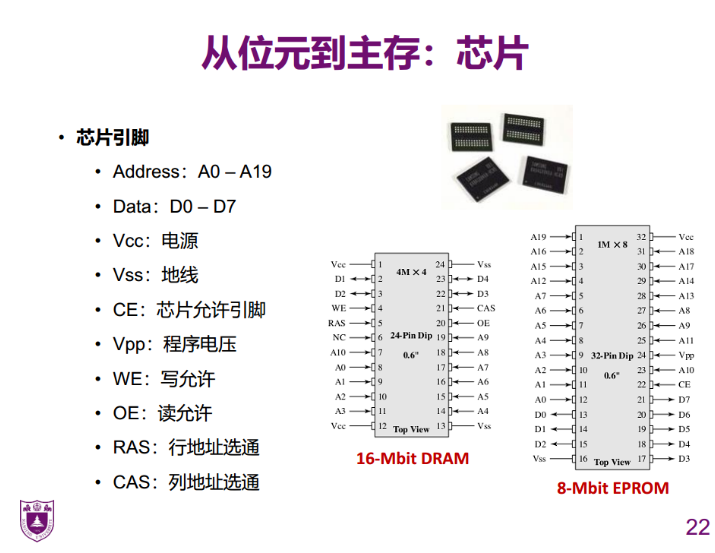

从位元到主存

寻址单元

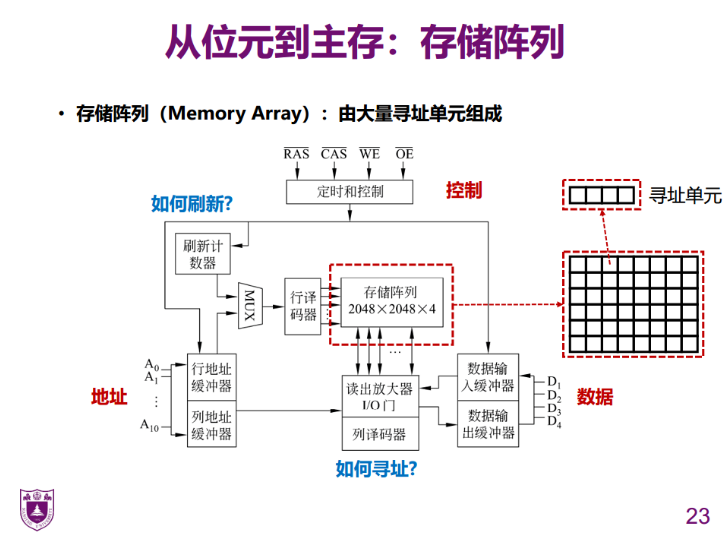

存储阵列

- 对于100个寻址单元构成的存储阵列,1100需要100根线;1010只需要20根线

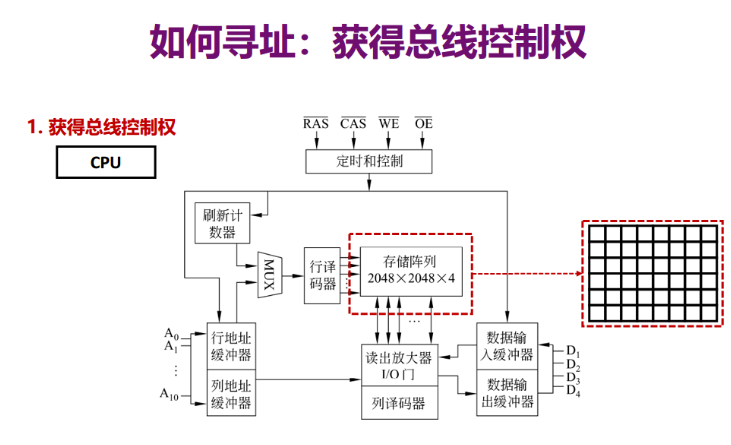

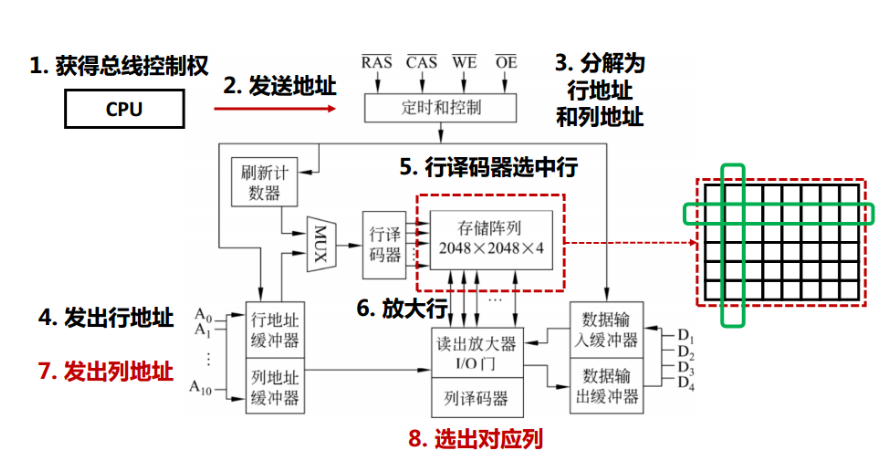

- 缓冲器:进行行地址和列地址的复用;在使用译码器进行解析

- 刷新计时器:内存主要由DRAM组成,由于电容的自然丢失,需要不断刷新

DRAM本身很大,引脚的使用量大,需要行列的复用

SRAM容量较小,不需要行列的复用

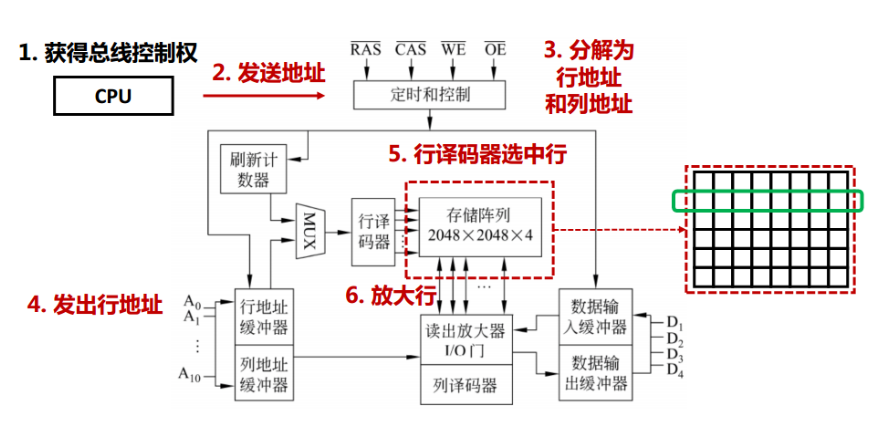

如何寻址:获得总线控制权

如何寻址:行访问

如何寻址:列访问

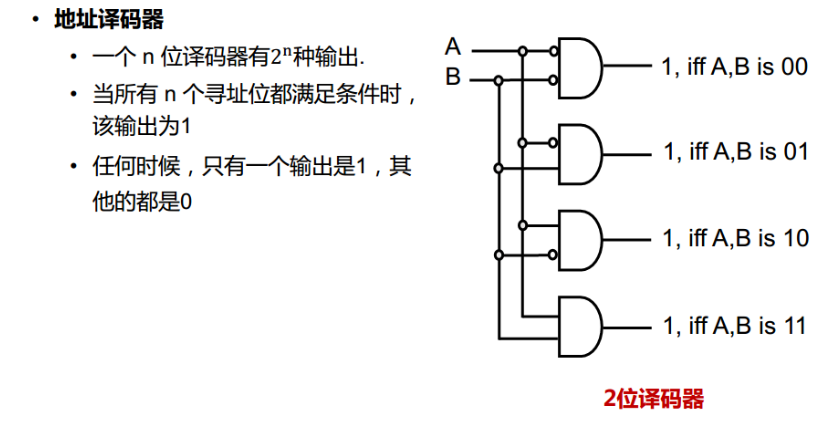

地址译码器

n位地址0101110……可以产生

刷新

- 集中式刷新:在具体的时间内,逐行刷新,但是停止CPU的读写操作了,内存一会工作一会不工作

- 分散式刷新:将集中分散到每一次读写操作中。刷新的时间和集中式刷新是差不多的,因为电容的流失不至于太快。不会出现不可访问的阶段

- 异步刷新:只要电容在一定时间内刷新即可,不被访问就刷新,一直被访问就强制刷新。读一行,刷另外一行

芯片

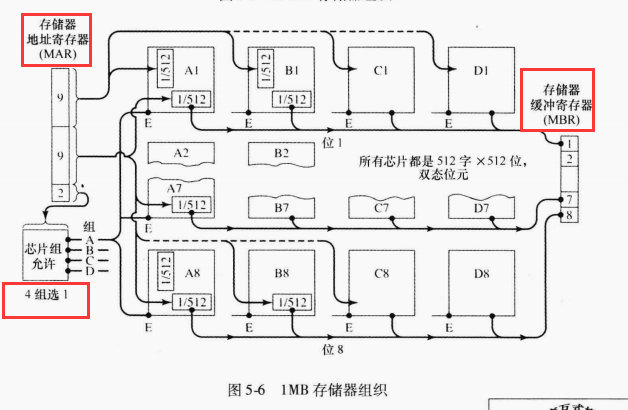

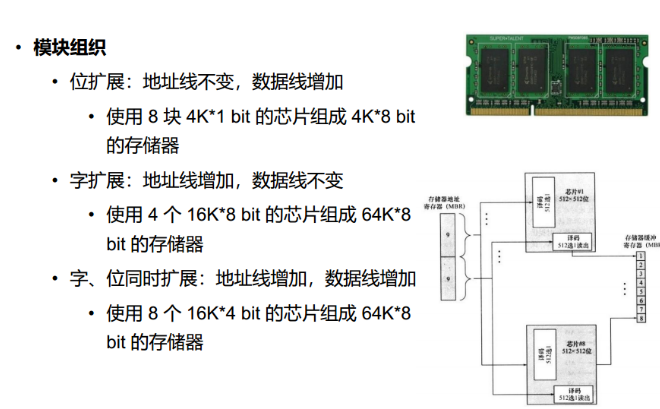

模块组织

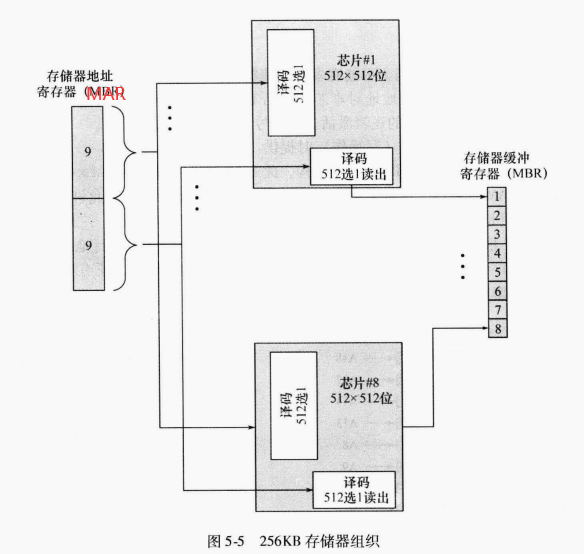

将芯片组织起来

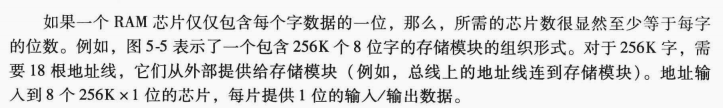

- 位扩展:寻址单元的个数没有变化,改变的是寻址单元内位元的个数/改变的是寻址模式

- 地址线决定的是有多少行、有多少列,此时不变

- 数据线的根数增加

- 字扩展:改变的是寻址单元的个数,不改变寻址单元内的位数

- 改变之前:如果行列复用,16k = 2^14需要7根地址线;改变后:64k = 2^16,需要8根地址线。地址线只多了一根,不复用的话多两根

- 字、位同时扩展:既增加寻址单元个数,也会增加寻址单元内的位数

- 复用多1根,不复用多2根

主存

红色、黄色:内存插槽,插入内存条

使用的是字扩展:可以访问的存储单元的个数增加了

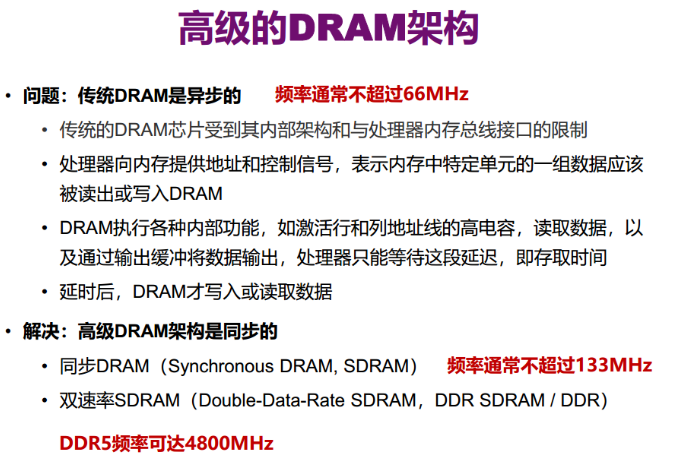

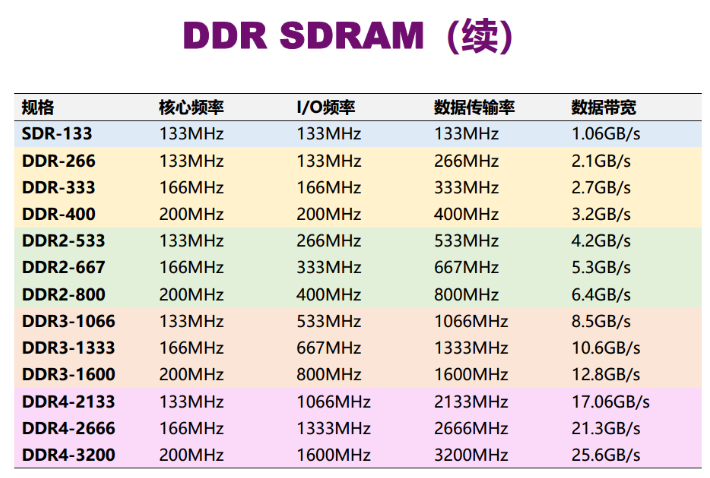

高级DRAM组织

同步DRAM SDARM

synchronous DRAM

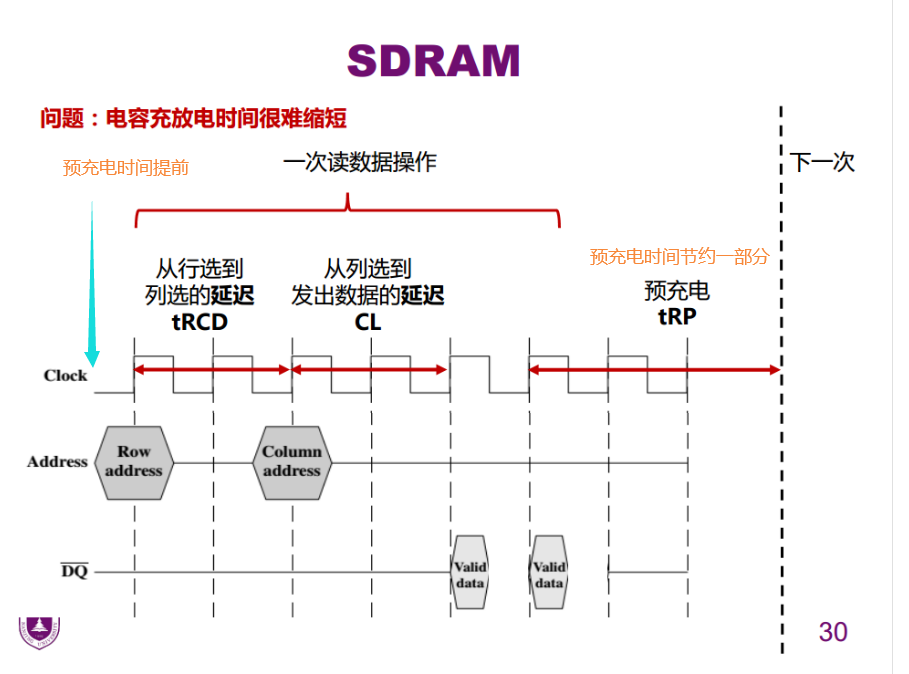

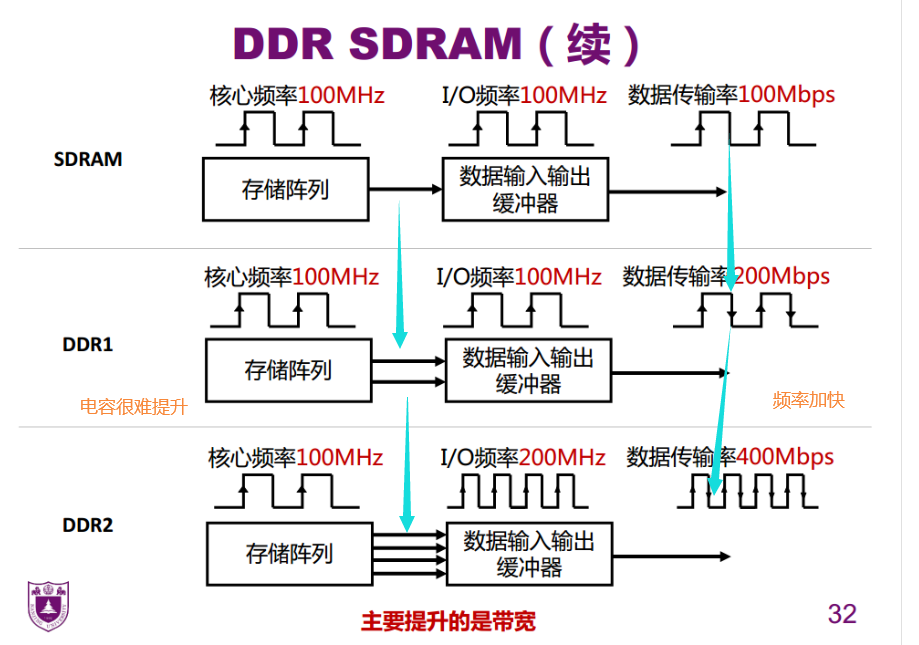

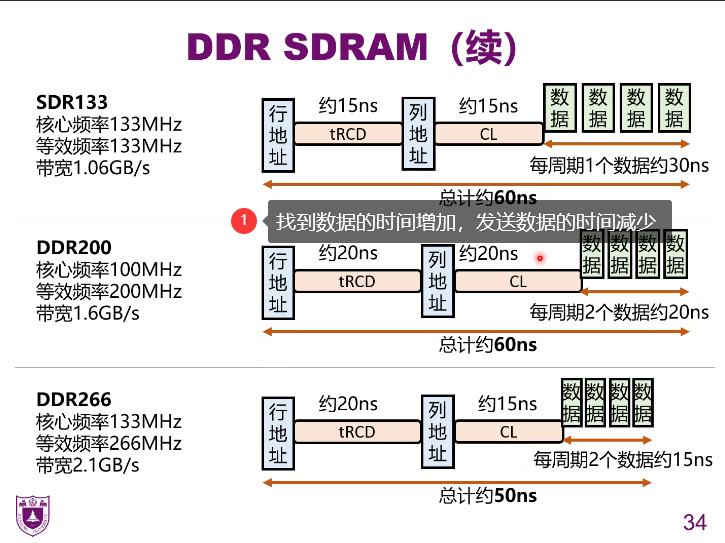

DDR SDRAM

增加数据带宽

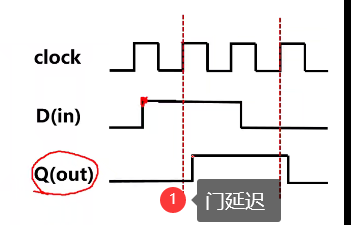

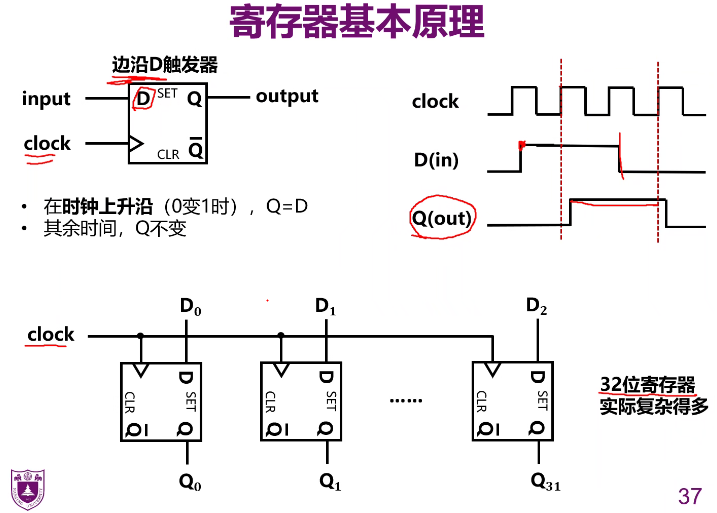

寄存器基本原理

- 连接在同一个时钟周期上,32位的变化是同步的

- 寄存器很快:和CPU的时钟周期是同步的

- 存储数据:用到的是RS锁存器(是实现SRAM的基础)